2 can 0 status register (c0s) -25 – Maxim Integrated MAXQ7666 User Manual

Page 155

MAXQ7665/MAXQ7666 User’s Guide

4-25

4.2.4.2 CAN 0 Status Register (C0S)

Register Description:

CAN 0 Status Register

Register Name:

C0S

Register Address:

Module 04h, Index 01h

The bits BSS, EC96, WKS, ER2, ER1, and ER0 in the CAN 0 status register are read-only by the microcontroller. The CAN processor

sets or clears these flags (and interrupt sources) as defined by the system aspects associated with each bit. A CAN status register

read clears the internal status-change interrupt flag. Unlike RXS and TXS, however, the individual mechanisms that set the ER2, ER0,

BSS, EC96, and WKS bits do not reoccur without first being removed by the CAN processor. As a result, a new (0

≥ 1) change by BSS,

EC96, or (1

≥ 0) change by WKS is required to set a new internal status-change interrupt flag through these bits. In a similar fashion,

a read of the CAN status register (which automatically sets ER2:ER0 to 111), followed by a new transmit or receive error, is required to

set a new internal status-change interrupt flag. If any one of these bits changes state from a previous 0 to 1 (other than WKS, which

changes from 1 to 0) and STIE is set to 1with no other interrupt pending, the INTIN vector in CAN interrupt register is set to 01h. If TXS

or RXS are set to 1 and a second message is successfully transmitted or received, and STIE is set to 1 while no other interrupt is pend-

ing, the INTIN vector in the CAN interrupt register is also set to 01h. If ER2:ER0 changes from either a 000 or 111, binary state to any

state other than 000 or 111, the INTIN vector in CAN interrupt register is also set to 01h. This issues a status-change interrupt request

if at least one of the conditions is valid and no other interrupt is pending.

Bits 15 to 8: Reserved. Read 0, write ignored.

Bit 7: CAN 0 Bus Status (BSS). (Read-only.) The BSS bit reflects the current status of the CAN 0 bus. When BSS = 1, the CAN 0 bus

is disabled (BUSOFF) and is not capable of receiving or transmitting messages. This condition is the result of the transmit-error counter

reaching a count of 256. When the CAN processor detects an error count of 256, the CAN processor automatically sets BSS = 1 and

clears SWINT = 0. BSS is cleared to 0 to enable CAN 0 bus activity when the CAN processor completes both the BUSOFF recovery

(128 x 11 consecutive recessive bits) and the power-up sequence (11 consecutive recessive bits). Once the CAN processor has com-

pleted this relationship, it sets SWINT = 1 and enters into the software initialization state. Once the microcontroller has cleared SWINT

to 0, the CAN processor is enabled to transmit and receive messages. BSS is set to 1 whenever the transmit-error counter for CAN 0

reaches the 256 limit. When BSS = 0, the CAN 0 bus is enabled to receive or transmit messages. A change in the state of BSS from a

previous 0 to 1 generates an interrupt if the ERIE, C0IE, IM4, and IGE* peripheral register bits are set. All microcontroller writes to the

SWINT bit are disabled when BSS = 1. Both the transmit- and receive-error counters are cleared to 00h when the BUSOFF condition

is cleared by the CAN module and BSS is cleared to 0.

Bit 6: CAN 0 Error Count Greater Than 96/128 Status (EC96/128). (Read-only.) The EC96/128 bit operates in one of two modes.

These two modes are determined by the state of the C0C.1 bit in the CAN 0 control register. Following a system or CAN reset, the

C0C.1 bit is cleared to 0, which in turn enables the EC96 mode.

C0C.1 = 0, EC96/128 = EC96. In this mode, when EC96/128 = 1 the interrupt flag indicates that either the CAN 0 transmit-error

counter or the CAN 0 receive-error counter has reached an error count of 96, which represents an exceptionally high number of

errors. EC96/128 = 0 indicates that the current transmit-error counter and receive-error counter both have an error count of less

than 96. A change in the state of EC96/128 from a previous 0 to 1 generates an interrupt if the ERIE, C0IE, IM4, and IGE* periph-

eral register bits are set. When C0C.1 is programmed to 1, the EC96/128 bit is reconfigured into an EC128 bit flag mode.

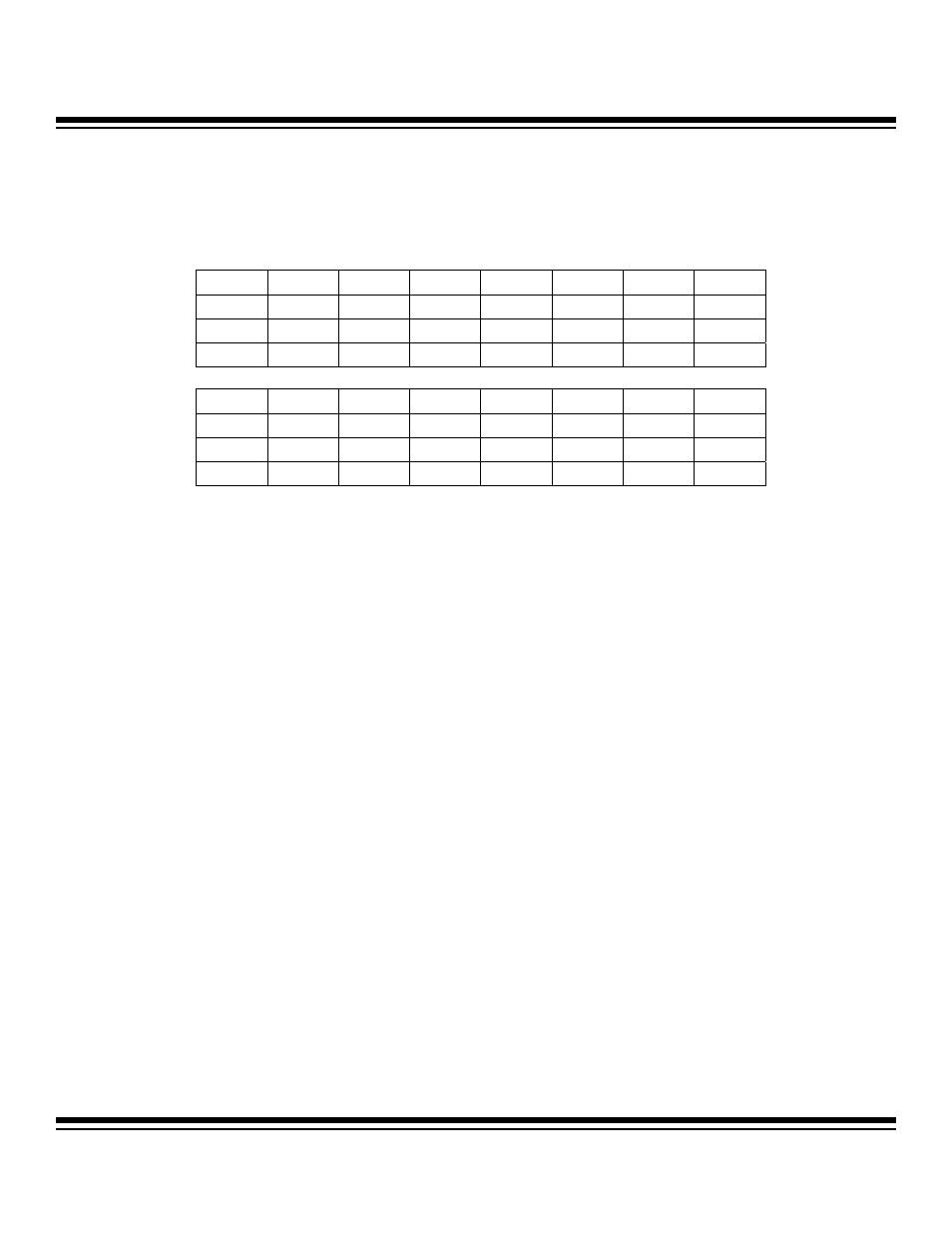

Bit #

15

14

13

12

11

10

9

8

Name

— — — — — — — —

Reset

0 0 0 0 0 0 0 0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

BSS

EC96/128

WKS RXS TXS ER2 ER1 ER0

Reset

0 0 0 0 0 0 0 0

Access r

r

r

rw

rw

rw

r

r

r = read, w = write

Maxim Integrated