Maxim Integrated MAXQ7666 User Manual

Page 204

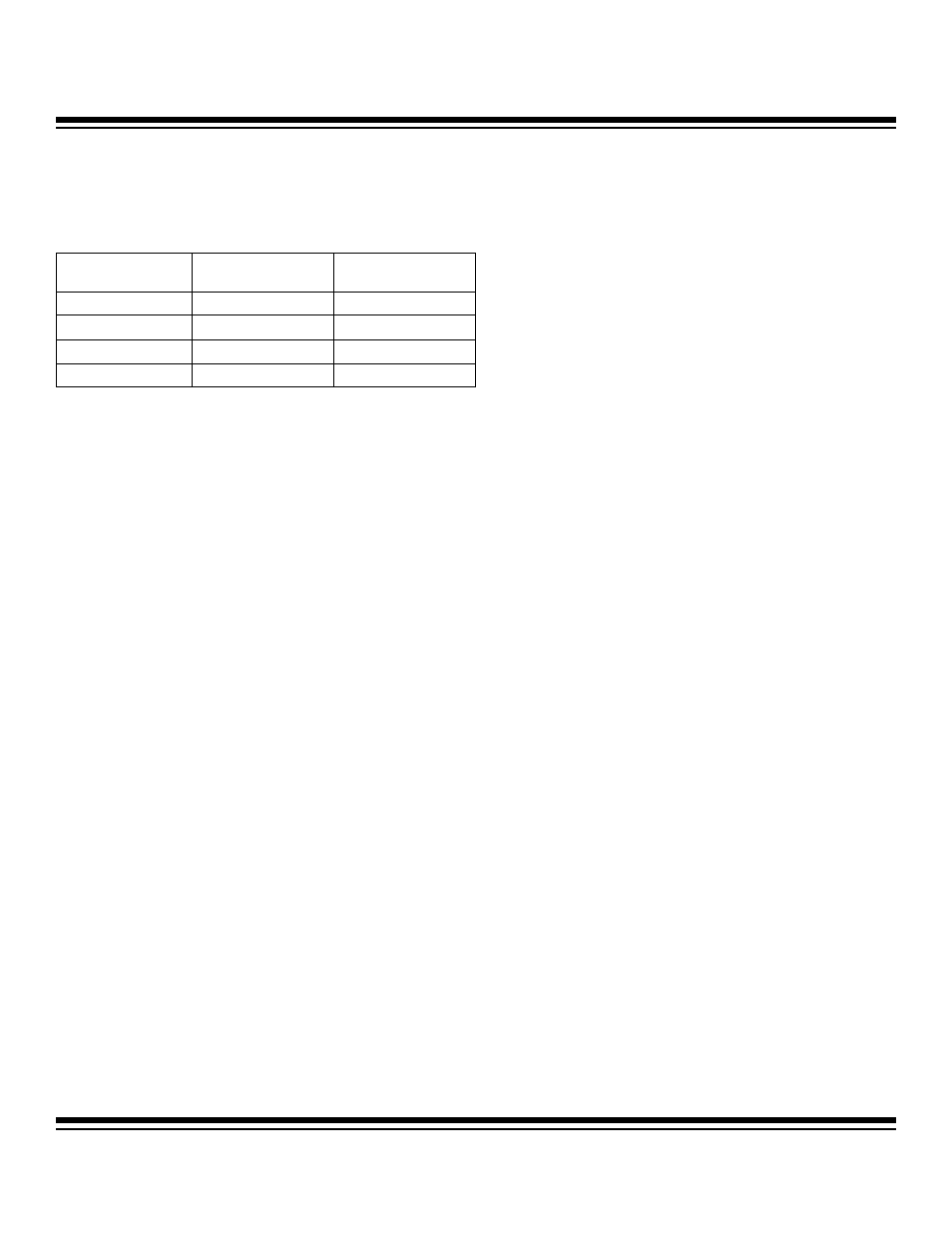

Bits 9 and 8: High-Frequency Crystal Input Capacitance Select 1 and 0 (HFIC1 and HFIC0). These bits select the input capaci-

tance of the on-chip high-frequency oscillator. The capacitor value is switched on to the XIN pin of the MAXQ7665. The possible selec-

tions are given below. Note: For the default 00 setting, only a 1.3pF capacitor is switched on. The 7pF capacitor value is essentially

due to stray capacitance.

Note: For the MAXQ7666, the HFIC1:HFIC0 bits set both the input and output capacitance. The HFOC1:HFOC0 bits are used to select

the crystal drive strength as previously explained.

Bits 7, 6, and 5: ADC Clock Divider Bits 2, 1, and 0 (ADCCD2, ADCCD1, ADCCD0). See

Section 3 for more information on these

bits.

Bit 2: External High-Frequency Clock Enable (EXTHF). Setting this bit to logic 1 enables direct input of the external high-frequency

clock to the XIN pin. Clearing this bit to logic 0 disables the high-frequency clock input. To use this as the system clock source, the XT

bit in the CKCN register must be set to logic 1.

Bit 1: Internal 7.6MHz RC Oscillator Enable (RCE). Setting this bit to logic 1 enables the internal 7.6MHz RC oscillator. Clearing this

bit to logic 0 disables the internal 7.6MHz RC oscillator. To use the internal 7.6MHz RC oscillator as the system clock source, the XT

bit in the CKCN register must be set to 0. In the MAXQ7665/MAXQ7666, the internal 7.6MHz RC oscillator is the default system clock

(RCE = 1, XT =0) after power-on reset. The watchdog timer is clocked by the internal 7.6MHz RC oscillator.

Note: The internal 7.6MHz RC oscillator is the default system clock source, so disabling it before the high-frequency crystal oscillator

is stable (XHFRY = 1) and selected as the system clock source (XT = 1) can cause unrecoverable system errors.

Bit 0: High-Frequency Crystal Oscillator Enable (HFE). Setting this bit to logic 1 enables the on-chip high-frequency oscillator for

use with an external crystal or resonator. Clearing this bit to 0 disables the high-frequency oscillator.

To use the external crystal or resonator as the system clock source, the HFE bit should first be set to logic 1 to allow the crystal oscil-

lator to power-up. At some time later, the XT bit of the CKCN register should be set to logic 1 to swap the system clock source from

the internal 7.6MHz RC oscillator to external crystal. If sufficient time has elapsed between setting HFE and setting XT to 1, the oscil-

lator is ready and the clock source will swap immediately. Otherwise, the crystal oscillator continues to power-up and the clock source

will swap to crystal when the power-up has completed. The XHFRY bit of the ASR indicates when the crystal oscillator circuit is ready

(XHFRY = 1), and the clock source can swap from the internal 7.6MHz RC oscillator to external crystal.

MAXQ7665/MAXQ7666 User’s Guide

5-7

HFIC1 HFIC0

CAPACITOR VALUE

(pF)

0 0

7

(default)

0 1 18

1 0 27

1 1 34

Maxim Integrated