Table 11-1. background mode commands -11, Table 11-1. background mode commands – Maxim Integrated MAXQ7666 User Manual

Page 307

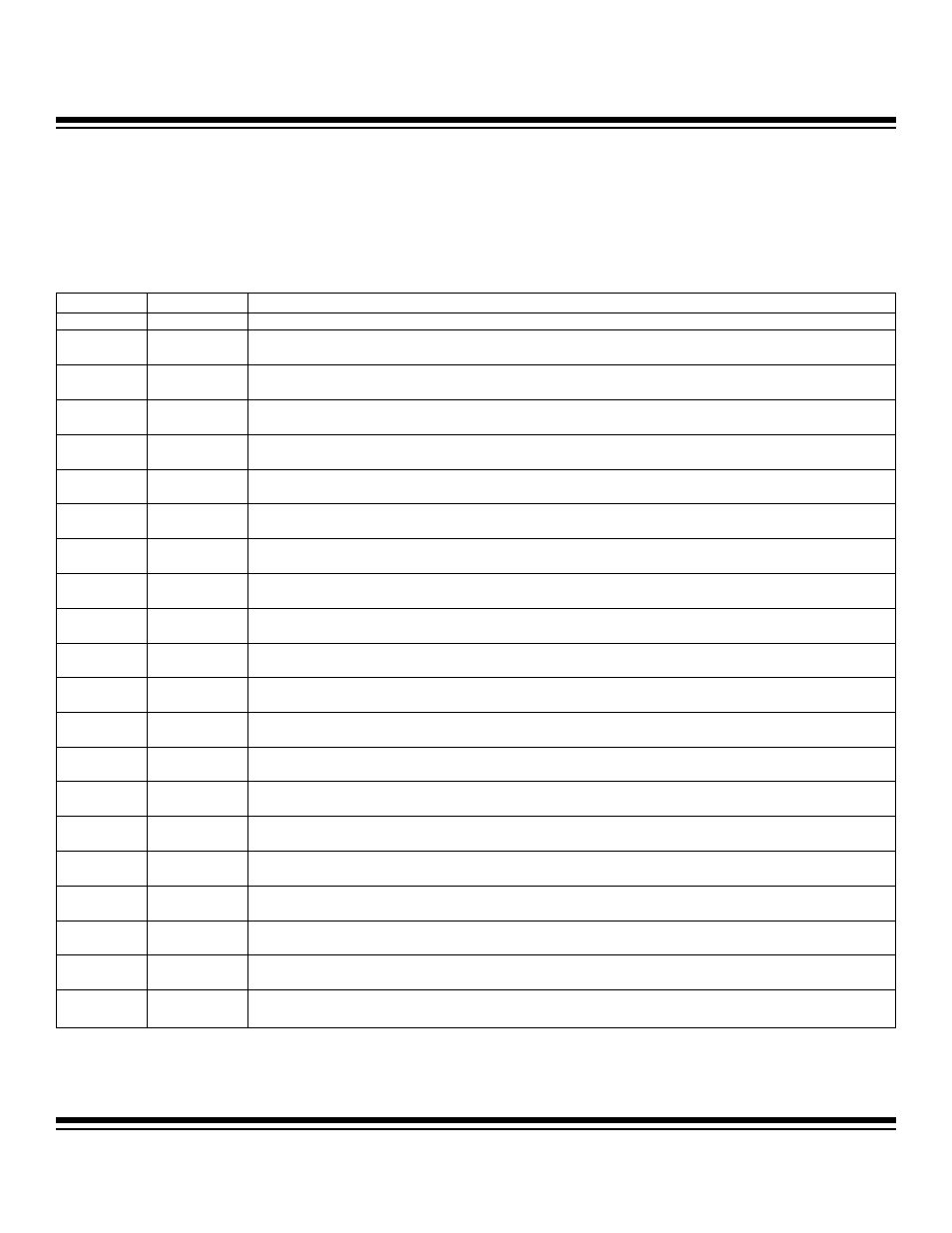

Table 11-1 shows the background mode commands supported by the MAXQ7665/MAXQ7666. Encodings not listed in this table are

not supported in background mode and are treated as no operations.

A command can consist of multiple-byte transactions between the external host and the debug engine via the TAP. However, a com-

mand code is always 8 bits and is always transmitted first, followed by address and/or data when needed.

MAXQ7665/MAXQ7666 User’s Guide

11-11

Table 11-1. Background Mode Commands

OP CODE

COMMAND OPERATION

0000-0000 No

Operation

No Operation. Default state for Debug Shift register.

0000-0001 Read

ICDC

Read Control Data from the ICDC. The contents of the ICDC register are loaded into the Debug Shift Register via the

ICDB register for host read. This command requires one follow-on transfer cycle.

0000-0010 Read

ICDF

Read Flags from the ICDF. The contents of the ICDF register (one byte) are loaded into the Debug Shift Register via the

ICDB register for host read. This command requires one follow-on transfer cycle.

0000-0011 Read

ICDA

Read Data from the ICDA. The contents of the ICDA register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-0100 Read

ICDD

Read Data from the ICDD. The contents of the ICDD register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-0101 Read

BP0

Read Data from the BP0. The contents of the BP0 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-0110 Read

BP1

Read Data from the BP1. The contents of the BP1 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-0111 Read

BP2

Read Data from the BP2. The contents of the BP2 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-1000 Read

BP3

Read Data from the BP3. The contents of the BP3 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-1001 Read

BP4

Read Data from the BP4. The contents of the BP4 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0000-1010 Read

BP5

Read Data from the BP5. The contents of the BP5 register are loaded into the Debug Shift Register via the ICDB

register for host read. This command requires two follow-on transfer cycles with the least significant byte first.

0001-0001 Write

ICDC

Write Control Data to the ICDC. The contents of ICDB are loaded into the ICDC register by the debug engine at the

end of the data transfer cycle.

0001-0011 Write

ICDA

Write Data to the ICDA. The contents of ICDB are loaded into the ICDA register by the debug engine at the end

of the data transfer cycles. Data is transferred with the least significant byte first.

0001-0100 Write

ICDD

Write Data to the ICDD. The contents of ICDB are loaded into the ICDD register by the debug engine at the end

of data transfer cycles. Data is transferred with the least significant byte first.

0001-0101 Write

BP0

Write Data to the BP0. The contents of ICDB are loaded into the BP0 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-0110 Write

BP1

Write Data to the BP1. The contents of ICDB are loaded into the BP1 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-0111 Write

BP2

Write Data to the BP2. The contents of ICDB are loaded into the BP2 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-1000 Write

BP3

Write Data to the BP3. The contents of ICDB are loaded into the BP3 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-1001 Write

BP4

Write Data to the BP4. The contents of ICDB are loaded into the BP4 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-1010 Write

BP5

Write Data to the BP5. The contents of ICDB are loaded into the BP5 register by the debug engine at the end of data

transfer cycles. Data is transferred with the least significant byte first.

0001-1111 Debug

Debug Command. This command forces the debug engine into debug mode and halts the CPU operation at the

completion of the current instruction after the debug engine recognizes the debug command.

Maxim Integrated