1 tap pins -4, Table 10-1. maxq7665/maxq7666 tap pins -4, 1 tap pins – Maxim Integrated MAXQ7666 User Manual

Page 290

MAXQ7665/MAXQ7666 User’s Guide

10-4

10.2.1 TAP Pins

The TAP is formed by four interface signals as described in Table 10-1. The TAP signals are multiplexed with port pins P0.0, P0.1, P0.2,

and P0.3. These pins default to their JTAG TAP function on reset, which means that the MAXQ7665/MAXQ7666 will always be ready

for in-circuit debugging or in-circuit programming following any reset.

Once an application has been loaded and starts running, the JTAG TAP port can still be used for in-circuit debugging operations. If

in-circuit debugging functionality is not needed, the P0.0, P0.1, P0.2, and P0.3 port pins can be reclaimed for application use by set-

ting the TAP (SC.7) bit to 0. This disables the JTAG TAP interface and allows the four pins to operate as normal port pins.

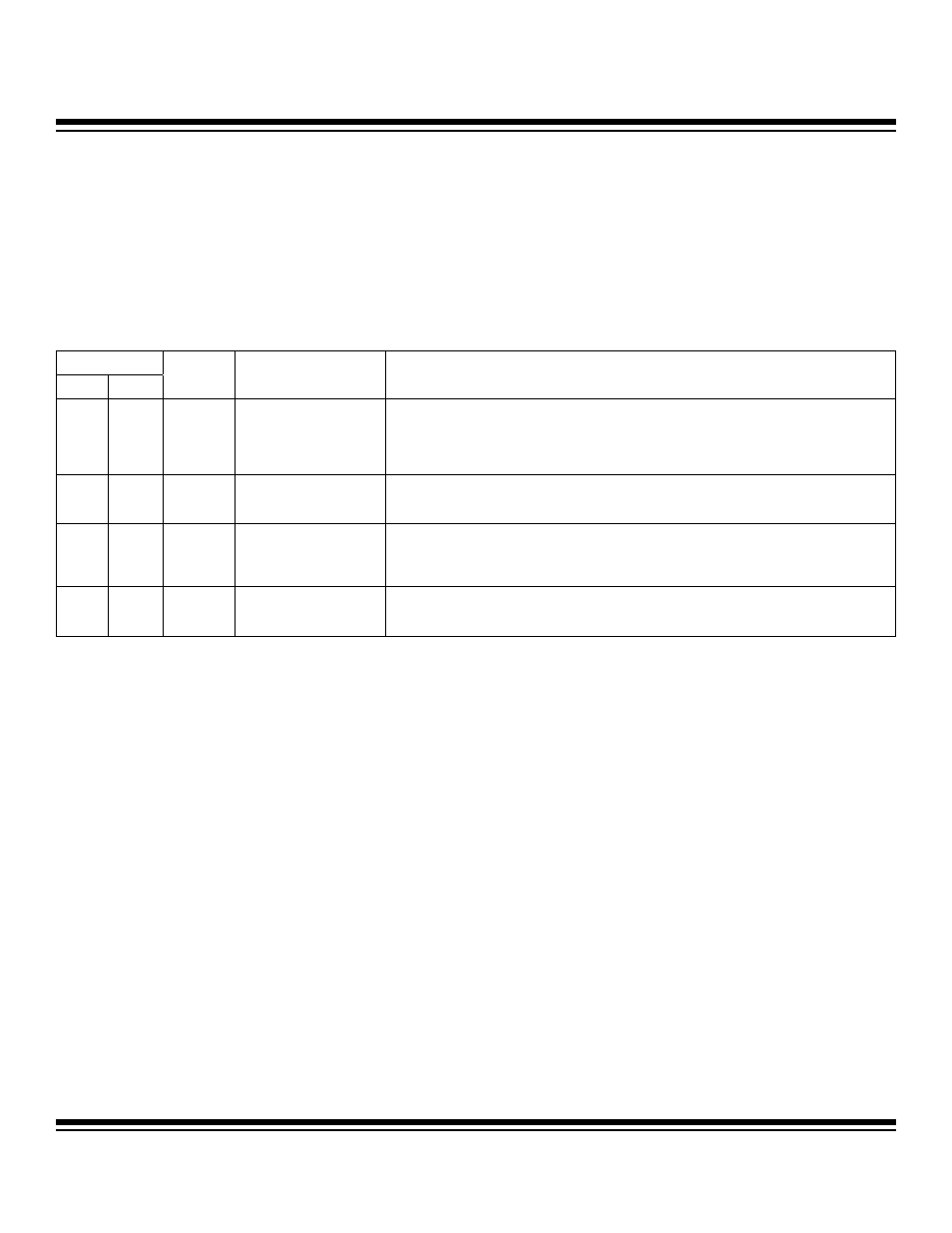

Table 10-1. MAXQ7665/MAXQ7666 TAP Pins

PIN

48

56

NAME

MULTIPLEXED WITH

PORT SIGNAL

FUNCTION

32

37

TDO

P0.0

JTAG Serial Test Data Output. This signal is used to serially transfer internal data to the

external host. Data is transferred least significant bit first. Data is driven out only on the

falling edge of TCK, only during TAP Shift-IR or Shift-DR states and is otherwise inactive.

This pin is weakly pulled high internally when inactive and/or when SC.7 (TAP) = 1. After

power-up or a reset this pin defaults to JTAG TDO pin.

33

38

TMS

P0.1

JTAG Test Mode Select Input. This signal is sampled at the rising edge of TCK and

controls movement between TAP states. TMS is weakly pulled high internally when TAP =

1. After power-up or a reset this pin defaults to JTAG TMS pin.

34

39

TDI

P0.2

JTAG Serial Test Data Input. This signal is used to receive data serially transferred by the

host. Data is received least significant bit first and is sampled on the rising edge of TCK.

TDI is weakly pulled high internally when TAP = 1. After power-up or a reset this pin

defaults to JTAG TDI pin.

35

40

TCK

P0.3

JTAG Serial Test Clock Input. Provided by the host. When this signal is stopped at 0,

storage elements in the TAP logic retain their data indefinitely. TCK is weakly pulled high

internally when TAP = 1. After power-up or a reset this pin defaults to JTAG TCK pin.

Maxim Integrated