4 watchdog timer control register (wdcn) -10, 4 watchdog timer control register (wdcn) – Maxim Integrated MAXQ7666 User Manual

Page 207

MAXQ7665/MAXQ7666 User’s Guide

5-10

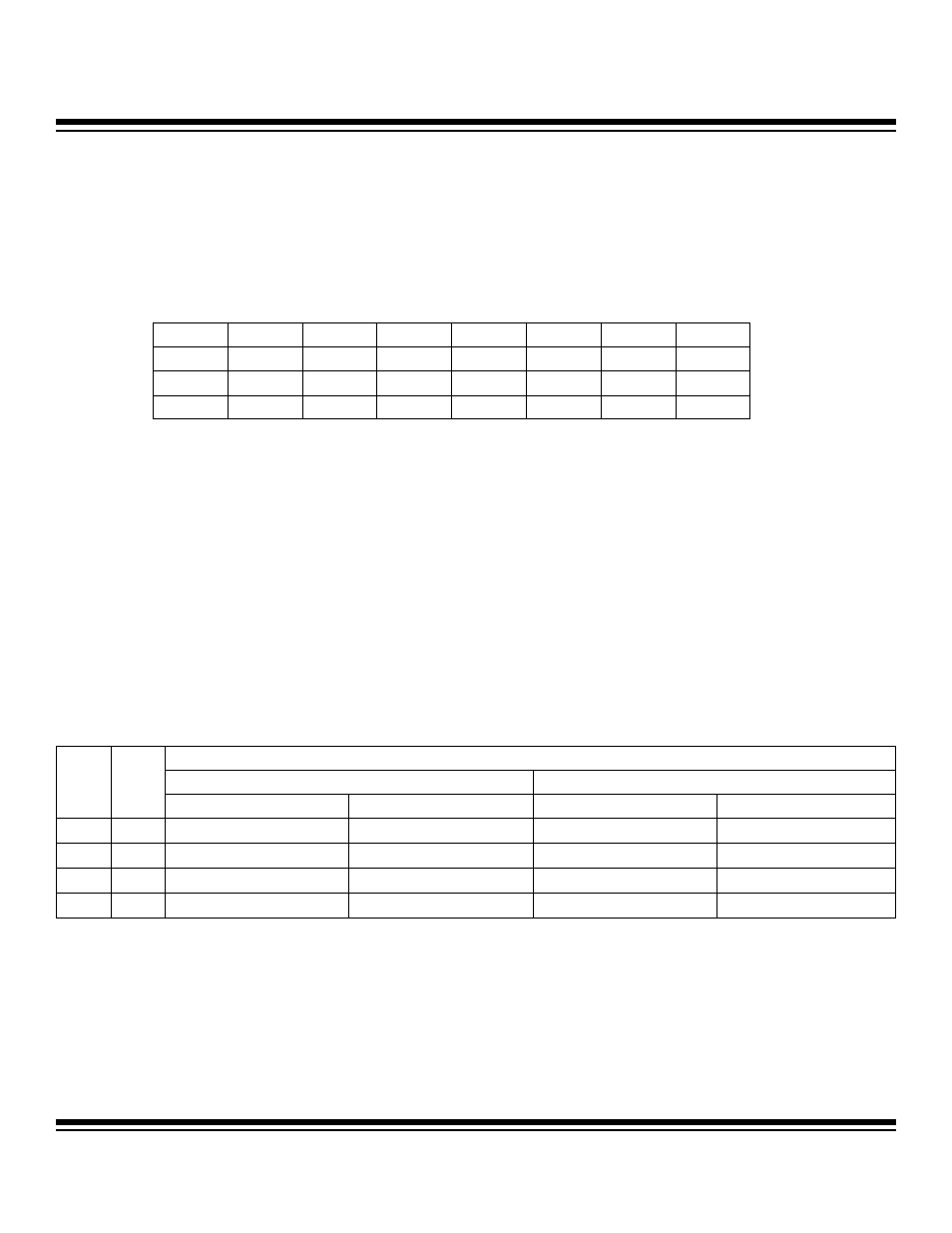

5.2.4 Watchdog Timer Control Register (WDCN)

The 8-bit WDCN register is part of the system register group and used to provide system control. It controls the watchdog timeout peri-

od and interrupt or reset generation on watchdog timeout. The watchdog timer is clocked by the internal 7.6MHz RC oscillator. Enabling

the watchdog does not force the internal 7.6MHz RC oscillator enable (RCE) bit to logic 1.

Register Description:

Watchdog Timer Control Register

Register Name:

WDCN

Register Address:

Module 08h, Index 0Fh

Bit 7: Power-On Reset Flag (POR). This bit is set to 1 whenever a power-on reset occurs. It is unaffected by other forms of reset. This

bit can be checked by software following a reset to determine if a power-on reset occurred. It should always be cleared by software

following a reset so that the source of the next reset can be correctly determined by software.

Bit 6: Watchdog Interrupt Enable (EWDI). If this bit is set to 1, an interrupt request can be generated when the WDIF bit is set to 1

by any means. If this bit is cleared to 0, no interrupt will occur when WDIF is set to 1; however, it does not stop the watchdog timer or

prevent watchdog timer resets from occurring if EWT = 1. If EWT = 0 and EWDI = 0, the watchdog timer will be stopped. If the watch-

dog timer is stopped (EWT = 0 and EWDI = 0), setting the EWDI bit resets the watchdog interval and reset counter, and enables the

watchdog timer. This bit is cleared to 0 by power-on reset and is unaffected by other forms of reset.

Note: The watchdog timer is clocked by the internal 7.6MHz oscillator. Therefore, RCE must be set to 1 for the watchdog timer

operation.

Bits 5 and 4: Watchdog Timer Mode Select Bits 1 and 0 (WD1 and WD0). These bits determine the watchdog interval or the length

of time between resetting of watchdog timer and the watchdog generated interrupt in terms of RC clocks. Modifying the watchdog

interval via the WD1:WD0 bits automatically resets the watchdog timer unless the 512 RC clock reset counter is already in progress,

in which case, changing the WD1:WD0 bits does not affect the watchdog timer or reset counter.

Bit 3: Watchdog Interrupt Flag (WDIF). This flag is set to 1 when the watchdog timer interval has elapsed or can be set to 1 by user

software. When WDIF = 1, an interrupt request is generated if the watchdog interrupt has been enabled (EWDI = 1) and not otherwise

masked or prevented by an interrupt already in service (i.e., IGE = 1, IMS = 1, and INS = 0 must be true for the interrupt to occur). This

bit should be cleared by software before exiting the interrupt service routine to avoid repeated interrupts. Furthermore, if the watchdog

reset has been enabled (EWT = 1), a reset is scheduled to occur 512 RC clock cycles following setting of the WDIF bit.

Bit #

7

6

5

4

3

2

1

0

Name

POR EWDI WD1 WD0 WDIF WTRF EWT RWT

Reset 0 0 0 0 0 0 0 0

Access rw rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: Bits 5, 4, 3, and 0 are cleared to 0 on all forms of reset; for others, see the individual bit descriptions.

WATCHDOG TIMEOUT PERIOD

RC CLOCKS

MILLISECONDS (FOR RC = 7.6MHz)

WD1

WD0

UNTIL INTERRUPT

UNTIL RESET

UNTIL INTERRUPT

UNTIL RESET

0 0

2

12

(default)

2

12

+ 2

9

0.539 0.606

0 1

2

15

2

15

+ 2

9

4.31 4.38

1 0

2

18

2

18

+ 2

9

34.49 34.56

1 1

2

21

2

21

+ 2

9

275.94 276.01

Maxim Integrated