Maxim Integrated MAXQ7666 User Manual

Page 100

Bits 2 to 0: ADC Source Select Bits 2 to 0 (ADCS2 to ADCS0). These bits select the ADC conversion start source used to trigger

analog-to-digital conversion:

In mode 110, the ADC completes a conversion every 16 clocks with a PGA gain of 1. For other gains the PGA is active and conver-

sions complete every 56 clocks.

Note that the ADC conversion start source could be one of the timers, ADC conversion start pin, or software writes to ADC start bit. All

three conversion start sources support single-edge or dual-edge modes of operation. Single- or dual-edge mode is controlled by ADC-

DUL bit. Also, all three conversion start sources support auto-shutdown after a conversion. See the ADCASD control bit description.

Note: It is recommended that the ADCS bits are updated before triggering conversions so the ADC conversion start source selection

fully takes effect. As an example, the ADCBY bit should not be set in the same ACNT register write which changes the ADCS bits to

111. The same recommendation also applies to other conversion start sources. When the ADCS bits are being updated, avoid gener-

ating an ADC conversion trigger from the timers or the ADC conversion start pin.

MAXQ7665/MAXQ7666 User’s Guide

3-10

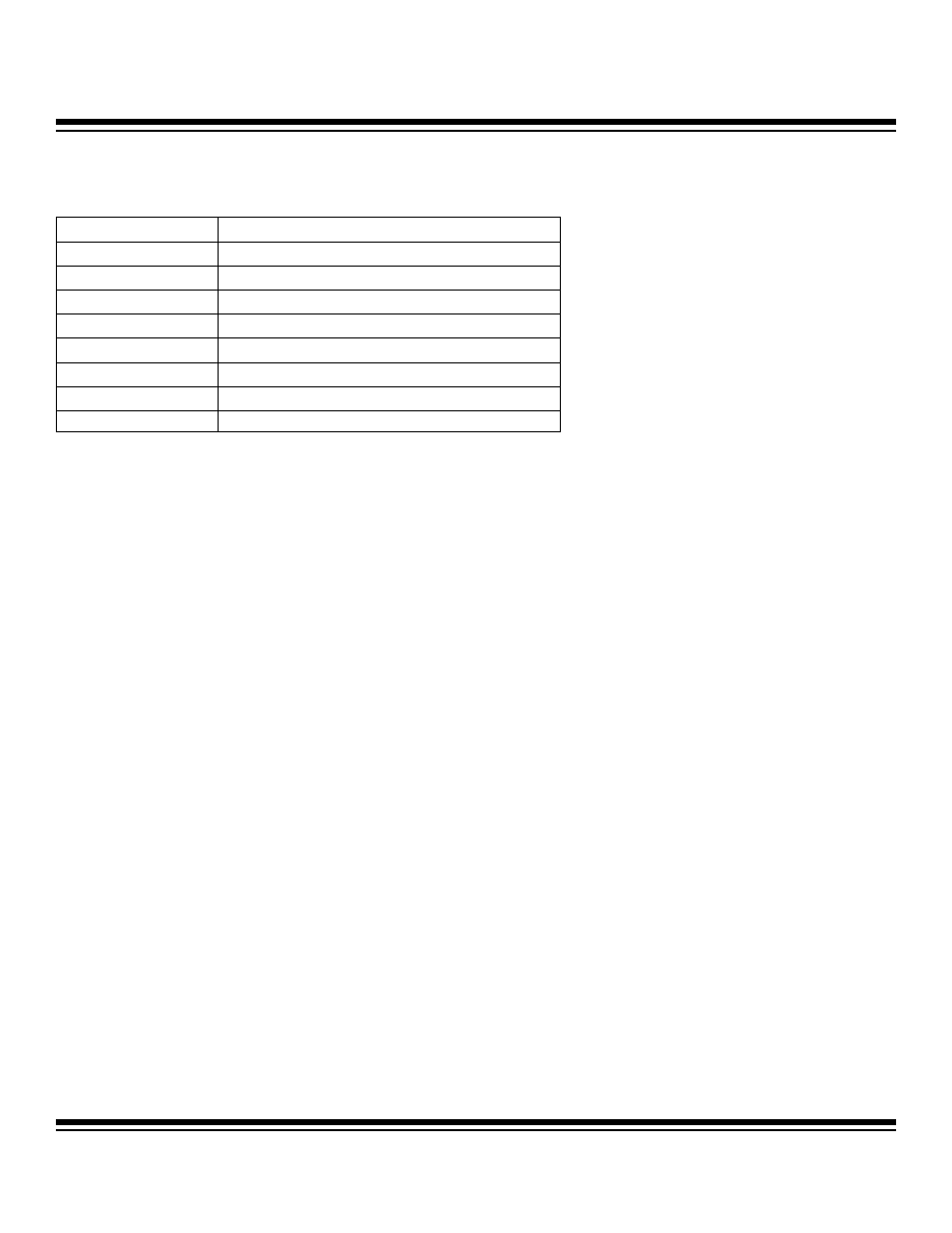

ADCS2:ADCS0

CONVERSION START SOURCE

000 Timer

0.

001 Timer

1.

010 Timer

2.

011

Reserved, functions as 010 if set.

100

From ADC conversion start pin: P0.4/ADCCNV.

101

From ADC conversion start pin with inverted data.

110

Continuous conversion every 16 clocks.

111

From ADC start bit: ACNT.3.

Maxim Integrated