Maxim Integrated MAXQ7666 User Manual

Page 141

MAXQ7665/MAXQ7666 User’s Guide

4-11

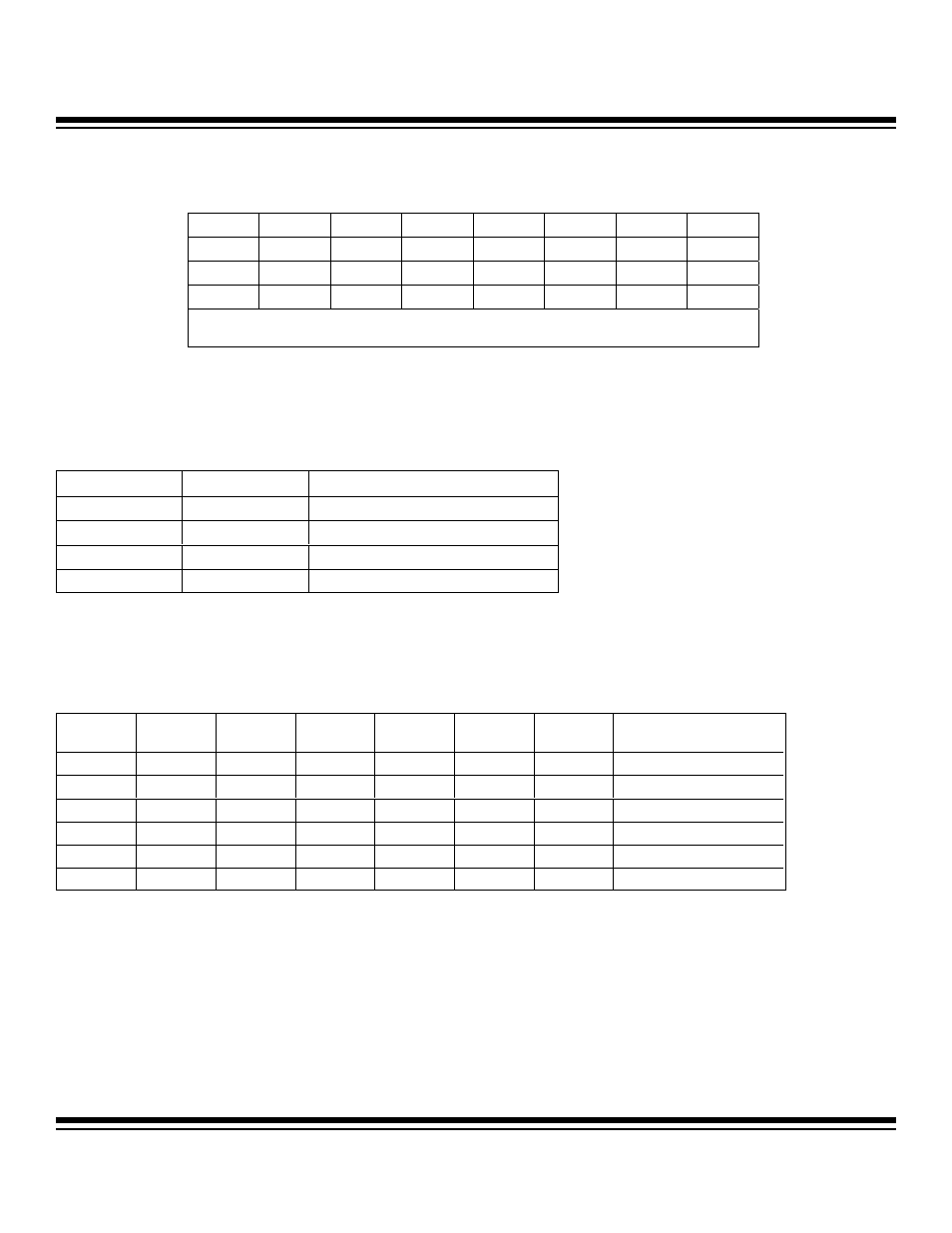

CAN 0 Bus Timing Register 0 (C0BT0)

Bits 7 and 6: CAN Synchronization Jump Width Select (SJW1 and SJW0). These bits specify the maximum number of time quan-

ta (t

QU

) cycles that a bit can be lengthened or shortened in one resynchronization to compensate for phase errors detected by the

CAN controller when receiving data. These bits can only be modified during a software initialization (SWINT = 1).

Bits 5 to 0: CAN Baud-Rate Prescaler (BPR5 to BPR0). These bits specify the lower six bits (BPR5–BRR0) of the 8-bit prescale value

(BPR7–BPR0). The 256 states defined by the binary combinations of the BPR7–BPR0 bits determine the value of the prescale, which

in turn defines the cycle time associated with one time quanta. These bits can only be modified during a software initialization (SWINT

= 1). The BPR7, BPR6 bits are located in the COR peripheral register.

r = read, w = write (allowed only when SWINT = 1 via C0DP/C0DB)

Bit #

7 6 5 4 3 2 1 0

Name

SJW1 SJW0 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0

Reset

0 0 0 0 0 0 0 0

Access

rw rw rw rw rw rw rw rw

Dual Port

Address

02h(L)

SJW1

SJW0

SYNCRHONIZATION JUMP WIDTH

0

0

1 t

QU

(1)

0

1

2 t

QU

(2)

1

0

3 t

QU

(3)

1

1

4 t

QU

(4)

BPR7,

BPR6

BPR5

BPR4

BPR3

BPR2

BPR1

BPR0

BAUD-RATE PRESCALE

VALUE (BRPV)

00

0

0

0

0

0

0

1

00

0

0

0

0

0

1

2

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

11

1

1

1

1

1

0

255

11

1

1

1

1

1

1

256

Note: Number in parentheses is the SJW value used in bit timing calculations.

Maxim Integrated