Maxim Integrated MAXQ7666 User Manual

Page 160

MAXQ7665/MAXQ7666 User’s Guide

4-30

To properly reflect the value of each interrupt source in the C0IR register, each source must be enabled via the respective interrupt

enable. These include ERIE and/or STIE enable in the case of status-change-related interrupt (01) sources, and either the ETI or ERI

enable for each message center interrupt (02h–10h) source. The status values of the interrupt sources in C0IR do not, however, require

setting either the EA or C0IE bits in the IE and EIE peripheral registers.

There are two methods for verifying message center interrupts. One method uses the ETI/ERI interrupt enables within each CAN mes-

sage control register, and the other method uses the STIE interrupt enable in the CAN status register.

STIE = 1: When a transmission or a reception by the corresponding message center was successfully completed, the status

change interrupt and the RXS/TXS bit are asserted. To understand how each bit in the status register acts as an interrupt source,

review the bit descriptions of each bit in the status register. Note that a successful receive in relation to the RXS bit is dependent

on the AUTOB bit (AUTOB = 1 is successful receive only and AUTOB = 0 is successful receive and store). This is not the case

with the following ERI relationship, in which a receive is considered a successful receive only if the data was stored in the respec-

tive message center. The STIE interrupt method requires the microcontroller to poll each message center to establish the respec-

tive interrupt source following each status change interrupt.

ETI = 1 and/or ERI = 1: When a successful transmission or a successful reception and store by the corresponding message cen-

ter are completed, the interrupt is asserted according to its priority. This method relies on the hardwired priority of the message

centers. Minimal microcontroller intervention is required.

Terms used in the following descriptions:

Value A: Value that was indicated before and is not zero.

MCV (Message Center’s Value): Interrupt indicator value that corresponds to the message center that received or transmitted a mes-

sage, i.e., 02 for MC15, 03 for MC1, etc.

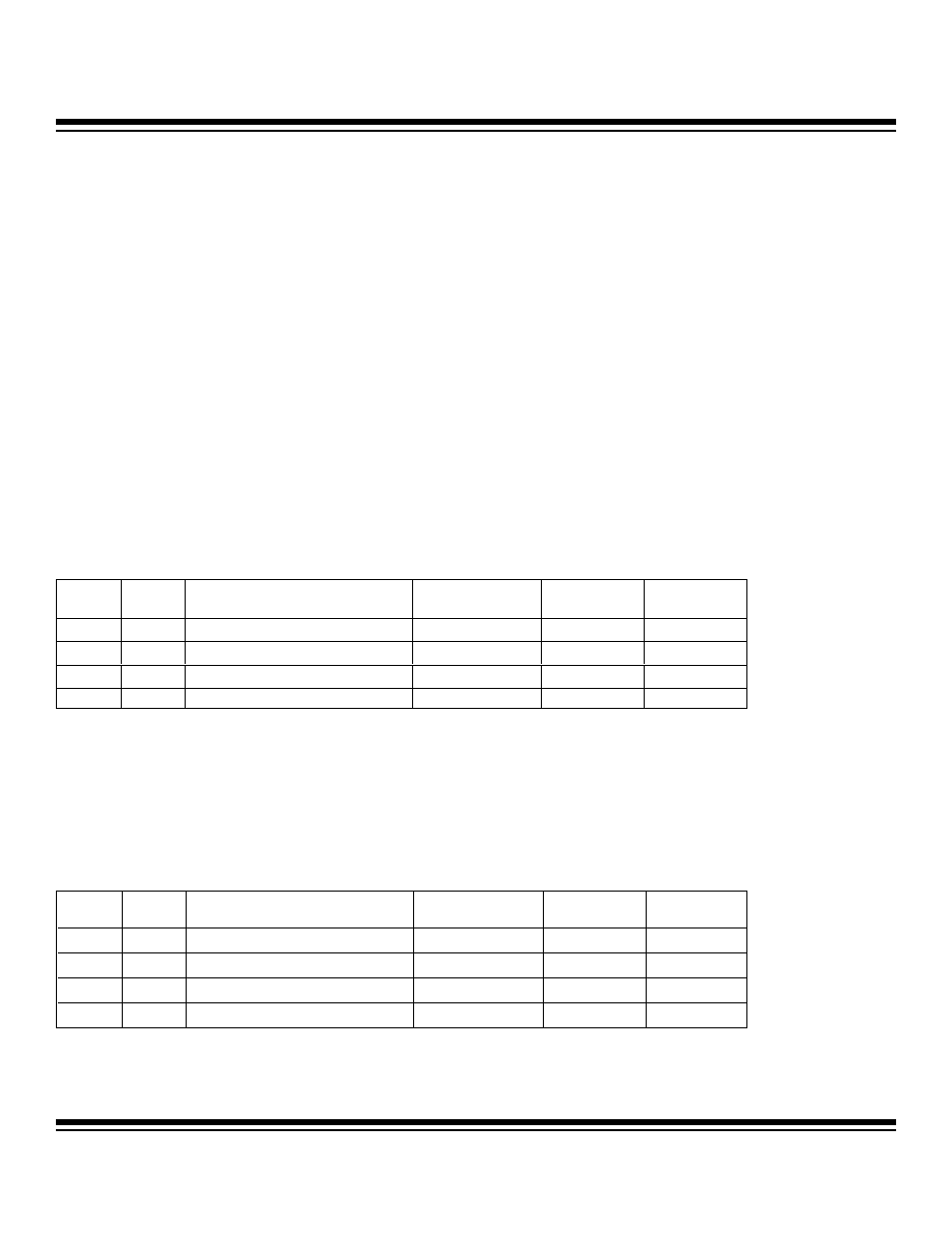

1a. STIE = 1 Only (Polling Method: ETI = ERI 0) with No Prior Interrupt Active

It is important to note that additional changes in bits 4–0 (RXS, TXS) of the CAN 0 status register can be detected even if these bits

have not been cleared by the microcontroller. The only requirement for the second status-change interrupt is for the microcontroller to

read the CAN 0 status register to clear the previous interrupt. Multiple changes in the CAN 0 status register, which are read from the

CAN 0 status register and occur without the microcontroller clearing the status-change interrupt, appear as one interrupt. The WKS bit

is a read-only bit and is not altered by a write from the microcontroller. The ER2:ER0 bits are automatically set to 111 following a read

of the CAN status register.

Although not related to a successful transmission or reception, ERIE =1 also enables a similar interrupt relationship when bits 6 or 7

are changed in the CAN status register, with ERIE = 1.

1b. ERIE = 1 with No Prior Interrupt Active

CASE

STIE

CHANGE DETECTED IN BITS 5:0

OF C0S PERIPHERAL REGISTER

INTIN VECTOR

INTRQ

CAN 0 INT

A

0

No

Value A or 0

Not affected

Inactive

B

0

Yes

Value A or 0

Not affected

Inactive

C

1

No

Value A or 0

Not affected

Inactive

D

1

Yes

Value A or 0 > 1

Not affected

Active

CASE

ERIE

CHANGE DETECTED IN BIT 7 OR 6

OF C0S PERIPHERAL REGISTER

INTIN VECTOR

INTRQ

CAN 0 INT

A

0

No

Value A or 0

Not affected

Inactive

B

0

Yes

Value A or 0

Not affected

Inactive

C

1

No

Value A or 0

Not affected

Inactive

D

1

Yes

Value A or 0 > 1

Not affected

Active

Maxim Integrated