Correlation to p1 – Measurement Computing DBK Part 2 User Manual

Page 267

Correlation to P1

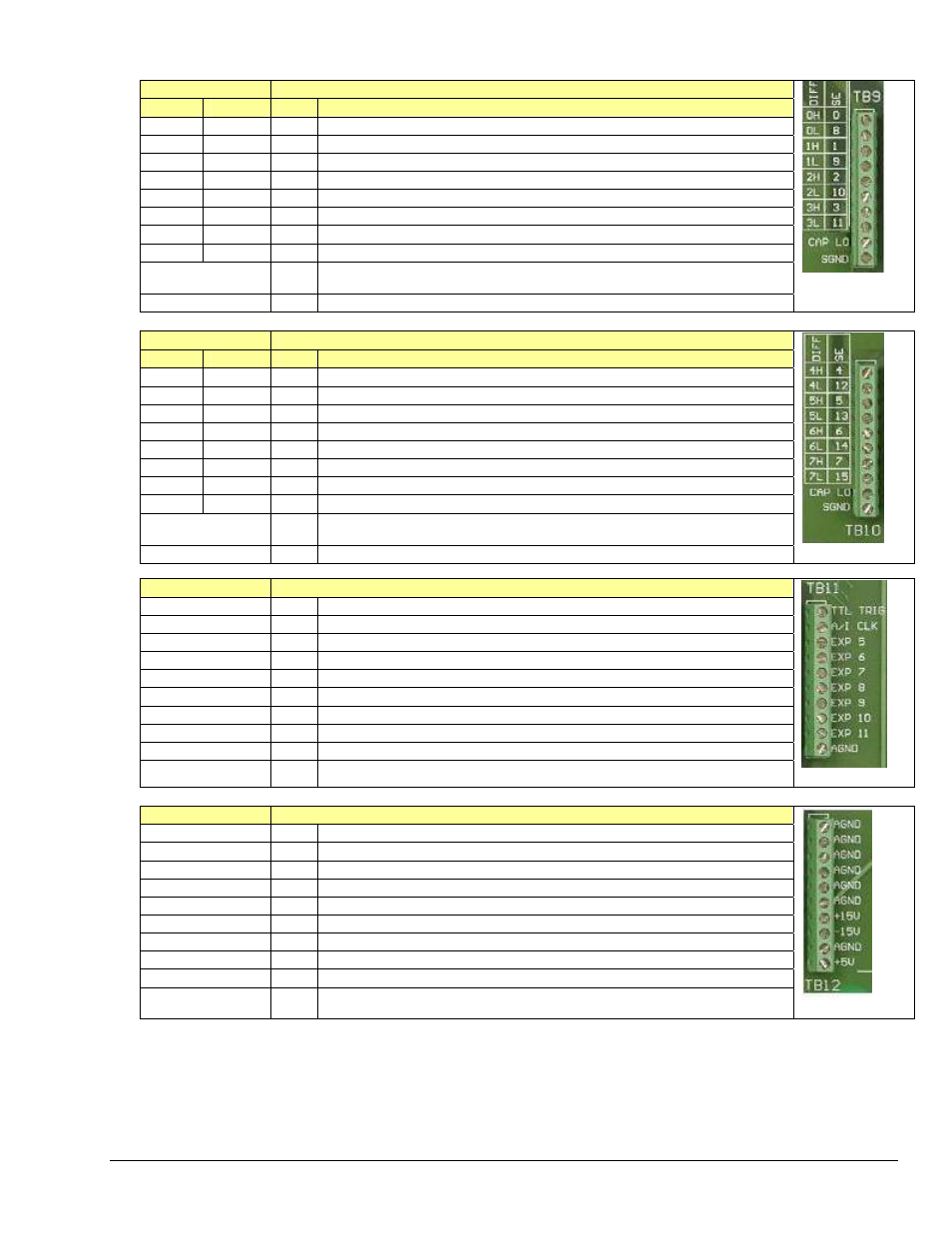

– Pertains to Terminal Blocks TB9, TB10, TB11, and TB12 for Analog I/O.

TB9

P1 Pin Number and Description (see Note 1)

DIFF

SE

0H

0

37

CH 0 IN (Single-Ended Mode) / CH 0 HI IN (Differential Mode)

0L

8

18

CH 8 IN (Single-Ended Mode) / CH 0 LO IN (Differential Mode)

1H

1

36

CH 1 IN (Single-Ended Mode) / CH 1 HI IN (Differential Mode)

1L

9

17

CH 9 IN (Single-Ended Mode) / CH 1 LO IN (Differential Mode)

2H

2

35

CH 2 IN (Single-Ended Mode) / CH 2 HI IN (Differential Mode)

2L

10

16

CH 10 IN (Single-Ended Mode) / CH 2 LO IN (Differential Mode)

3H

3

34

CH 3 IN (Single-Ended Mode) / CH 3 HI IN (Differential Mode)

3L

11

15

CH 11 IN (Single-Ended Mode) / CH 3 LO IN (Differential Mode)

FILT CAP LO

N/A

For RC filter networks install a wire jumper between the relevant FILT CAP LO and

AGND. Note that there is no association between FILT CAP LO and P4.

SGND

19

Signal Ground, Sense Common; reference ground, not for general use.

P1 – TB9

TB10

P1 Pin Number and Description (see Note 1)

DIFF

SE

4H

4

33

CH 4 IN (Single-Ended Mode) / CH 4 HI IN (Differential Mode)

4L

12

14

CH 12 IN (Single-Ended Mode) / CH 4 LO IN (Differential Mode)

5H

5

32

CH 5 IN (Single-Ended Mode) / CH 5 HI IN (Differential Mode)

5L

13

13

CH 13 IN (Single-Ended Mode) / CH 5 LO IN (Differential Mode)

6H

6

31

CH 6 IN (Single-Ended Mode) / CH 6 HI IN (Differential Mode)

6L

14

12

CH 14 IN (Single-Ended Mode) / CH 6 LO IN (Differential Mode)

7H

7

30

CH 7 IN (Single-Ended Mode) / CH 7 HI IN (Differential Mode)

7L

15

11

CH 15 IN (Single-Ended Mode) / CH 7 LO IN (Differential Mode)

FILT CAP LO

N/A

For RC filter networks install a wire jumper between the relevant FILT CAP LO and

AGND. Note that there is no association between FILT CAP LO and P4.

SGND

19

Signal Ground, Sense Common; reference ground, not for general use.

P1 – TB10

TB11

P1 Pin Number and Description

TTL TRIG

25

TTL Trigger, Digital IN, External TTL Trigger Input

A/I CLK

20

A/I Clock, External ADC Pacer Clock Input/ Internal ADC Pacer Clock Output

EXP 5

5

Expansion 5. Digital OUT, external GAIN select bit 1

EXP 6

6

Expansion 6. Digital OUT, external GAIN select bit 0

EXP 7

3

Expansion 7. Digital OUT, external ADDRESS, select bit 3

EXP 8

22

Expansion 8. Digital OUT, external ADDRESS, select bit 2

EXP 9

4

Expansion 9. Digital OUT, external ADDRESS, select bit 1

EXP 10

23

Expansion 10. Digital OUT, external ADDRESS, select bit 0

EXP 11

26

Expansion 11. Simultaneous Sample and Hold (SSH)

AGND

*

Analog Ground, Common

P1 – TB11

TB12

P1 Pin Number and Description

AGND

*

Analog Ground, Common

AGND

*

Analog Ground, Common

AGND

*

Analog Ground, Common

AGND

*

Analog Ground, Common

AGND

*

Analog Ground, Common

AGND

*

Analog Ground, Common

+ 15 V

21

Expansion, +15 V Power

- 15 V

2

Expansion, -15 V Power

AGND *

Common

Ground

+ 5 V

1

Expansion, +5 V Power

P1 – TB12

*Refer to Ground Correlation Tables in the DBK Options Manual (457-0905), chapter 2, System Connections and Pinouts.

Note 1: For TB9 and TB10, the filter network portion of the silkscreen is not shown. Instead, the DIFF and SE channel

identifiers have been moved next to the screws for ease in identification.

DBK Option Cards and Modules

969294

DBK213, pg. 7