Status registers – GW Instek PEL-2000 Series Programming User Manual User Manual

Page 163

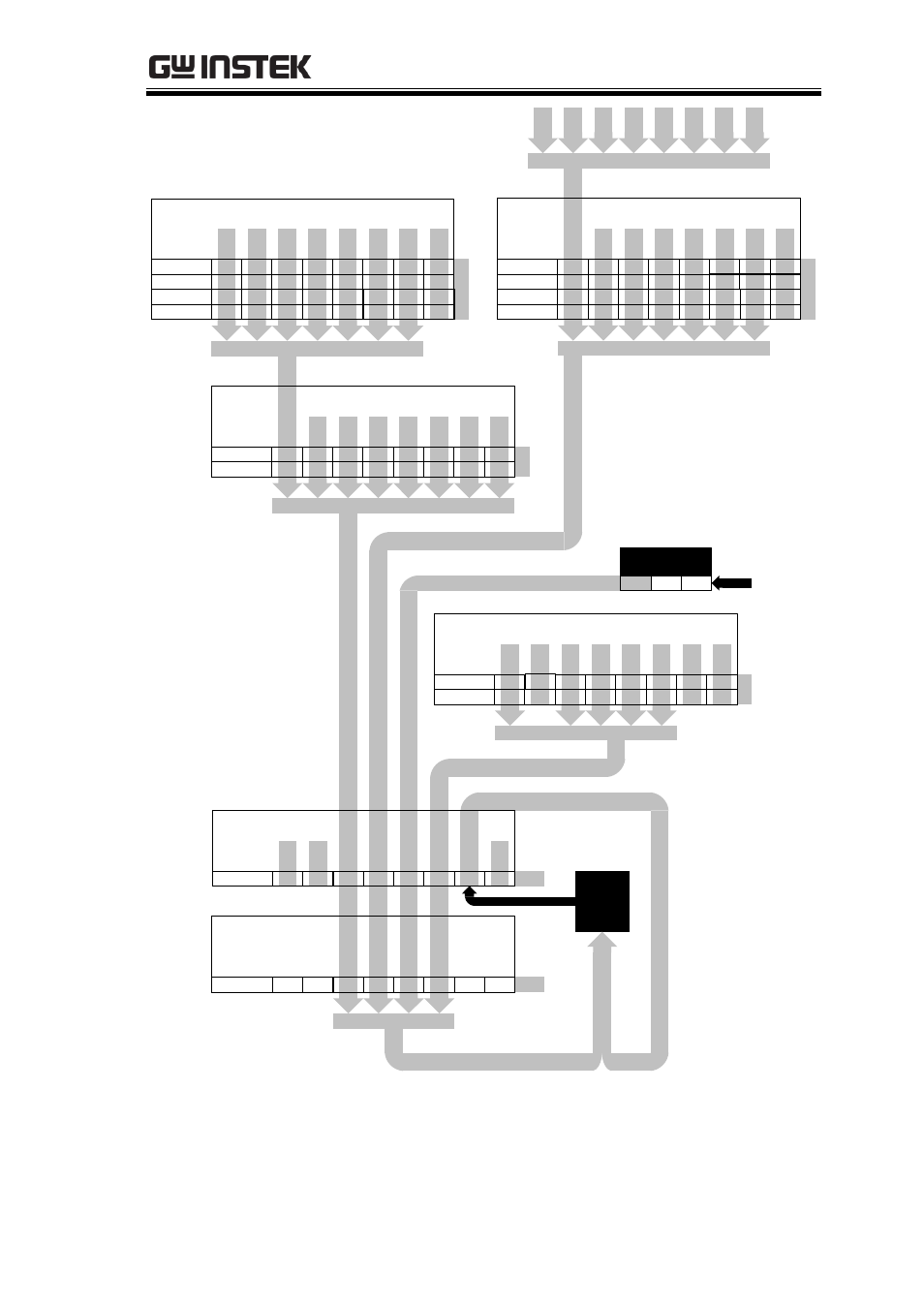

STATUS REGISTERS

163

B

IT

W

E

IG

H

T

1

2

4

8

OR

16

CONDITION

1

2

4

8

PTR/NTR

1

2

4

8

EVENT

1

2

4

8

ENABLE

OC

OV

OP

RV

OT

Protection

0

1

2

3

4

Bit position

B

IT

W

E

IG

H

T

1

2

4

8

16

EVENT

1

2

4

8

16

ENABLE

CH1

CH2

CH3

CH4

CH5

Channel

0

1

2

3

4

Bit position

32

64

128

32

64

128

CH6

CH7

CH8

5

6

7

B

IT

W

E

IG

H

T

1

2

4

8

OR

CONDITION

1

2

4

8

PTR/NTR

1

2

4

8

EVENT

1

2

4

8

ENABLE

OC

OV

OP

RV

Query

0

1

2

3

Bit position

OR

Questionable Status Registers

CH1 CH2 CH3 CH4 CH5

From

CH6 CH7 CH8

B

IT

W

E

IG

H

T

1

4

8

OR

Standard Event Status Registers

16

EVENT

1

4

8

16

ENABLE

OPC

N.U.

QYE

DDE

EXE

Message

0

1

2

3

4

Bit position

32

32

CME

N.U.

N.U.

5

6

7

Data

Data

Output Queue

Data

BIT

WEIGHT

4

8

16

STATUS BYTE

N.U.

N.U.

CSUM QUES

MAV

Status

0

1

2

3

4

Bit position

32

ESB

MSS

N.U.

5

4

8

OR

16

2

3

4

Bit position

32

5

Service Request Generation Register

CSUM QUES

MAV

ESB

BIT

WEIGHT

Service

Request

Generation

7

6

64

Status Byte Register

OR

Service

Request

Generation

Channel Summary Registers

32

G/N

5

64

UVP

6

N.U.

7-15

16

32

64

16

32

64

16

32

64

16

OT

4

32

G/N

5

64

UVP

6

N.U.

7-15

16

32

64

16

32

64

16

32

64

Channel Status Registers (Channel X)

- GDB-03 (99 pages)

- GLA-1000 Series User Manual (111 pages)

- GLA-1000 Series Quick start guide (20 pages)

- GOS-630FC (20 pages)

- GOS-635G (36 pages)

- GOS-6000 Series (27 pages)

- GOS-6103C (30 pages)

- GOS-6100 Series (30 pages)

- GRS-6000A Series (51 pages)

- GDS-122 Installation Guide (4 pages)

- GDS-122 User Manual (52 pages)

- GDS-2000A series CAN/LIN bus User Manual (18 pages)

- GDS-2000A series Quick start guide for DS2-FGN (6 pages)

- GDS-2000A series Freewave User Manual (26 pages)

- GDS-2000A series Quick start guide for Logic analyzer option (18 pages)

- GDS-2000A series Quick start quide for DS2-LAN (2 pages)

- GDS-2000A series Option User Manual (80 pages)

- GDS-2000A series User Manual (261 pages)

- GDS-2000A series Programming Manual (272 pages)

- GDS-2000A series Single sheet for LA Quick start guide (2 pages)

- GBS-1000 Series Programming Manual (88 pages)

- GBS-1000 Series User Manual (187 pages)

- GDS-1000-U Series firmware upgrade (1 page)

- GDS-1000-U Series Programming Manual (70 pages)

- GDS-1000-U Series Quick start guide (2 pages)

- GDS-1000-U Series User Manual (133 pages)

- GDS-1000A-U Series Programming Manual (88 pages)

- GDS-1000A-U Series Quick start guide (2 pages)

- GDS-1000A-U Series User Manual (148 pages)

- GDS-3000 Series GCP-530/1030 current probe User Manual (40 pages)

- GDS-3000 Series GDP-025/050/100 differential probe User Manual (21 pages)

- GDS-3000 Series DS3-PWR Power analysis manual (37 pages)

- GDS-3000 Series User Manual (209 pages)

- GDS-3000 Series Programming Manual (103 pages)

- GDS-3000 Series DS3-SBD Serial Bus decode (29 pages)

- GDS-3000 Series GKT-100 deskew fixture User Manual (1 page)

- GDS-3000 Series GUG-001, GPIB to USB adapter User Manual (15 pages)

- GDS-300 Series User Manual (188 pages)

- GDS-300 Series Programming Manual (139 pages)

- GDS-300 Series Quick start guide (21 pages)

- GRF-3300 Series Student Manual (26 pages)

- GRF-3300 Series Teacher Manual (26 pages)

- GRF-1300A (124 pages)

- GSP-810 User Manual (40 pages)

- GSP-810 Software Manual (3 pages)