Toshiba H1 Series User Manual

Page 78

TMP92CZ26A

92CZ26A-75

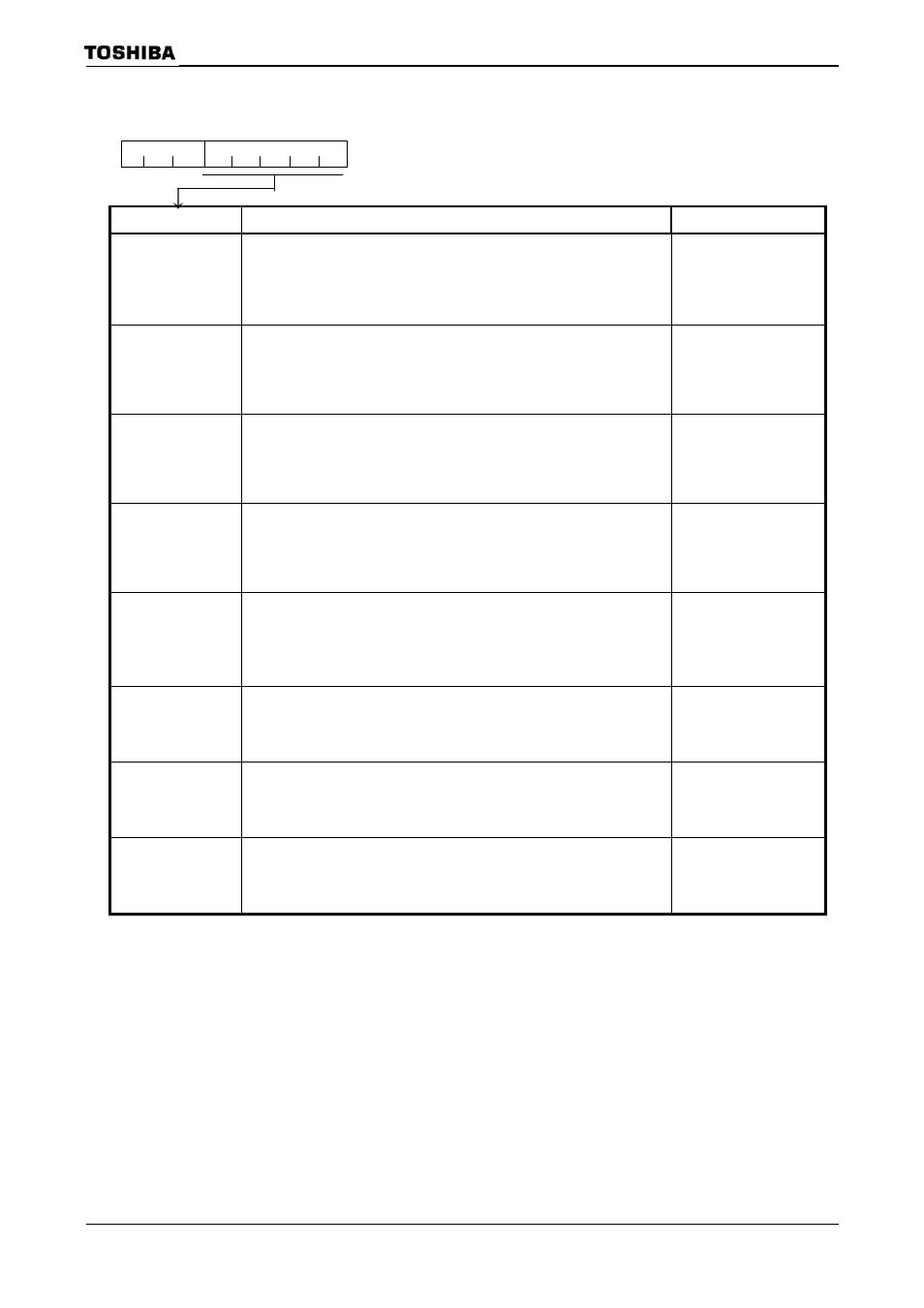

(4) Detailed description of the transfer mode register

0 0 0

Mode

DMAM0 to 7

DMAMn[4:0] Mode

Description Execution

Time

0 0 0 z z

Destination INC mode

(DMADn +)

← (DMASn)

DMACn

← DMACn - 1

if DMACn

= 0 then INTTCn

5 states

0 0 1 z z

Destination DEC mode

(DMADn -)

← (DMASn)

DMACn

← DMACn - 1

if DMACn

= 0 then INTTCn

5 states

0 1 0 z z

Source INC mode

(DMADn)

← (DMASn +)

DMACn

← DMACn - 1

if DMACn

= 0 then INTTCn

5 states

0 1 1 z z

Source DEC mode

(DMADn)

← (DMASn -)

DMACn

← DMACn – 1

if DMACn

= 0 then INTTCn

5 states

1 0 0 z z

Source and destination INC mode

(DMADn +)

← (DMASn +)

DMACn

← DMACn – 1

If DMACn

= 0 then INTTCn

6 states

1 0 1 z z

Source and destination DEC mode

(DMADn -)

← (DMASn -)

DMACn

← DMACn – 1

If DMACn

= 0 then INTTCn

6 states

1 1 0 z z

Destination and fixed mode

(DMADn)

← (DMASn)

DMACn

← DMACn – 1

If DMACn

= 0 then INTTCn

5 states

1 1 1 00

Counter mode

DMASn

← DMASn + 1

DMACn

← DMACn – 1

If DMACn

= 0 then INTTCn

5 states

ZZ:

00 = 1-byte transfer

01 = 2-byte transfer

10 = 4-byte transfer

11

=

Reserved

Note 1: n stands for the micro DMA channel number (0 to 7).

DMADn+/DMASn+: Post increment (Register value is incremented after transfer).

DMADn

−/DMASn−: Post decrement (Register value is decremented after transfer).

“I/O” signifies fixed memory addresses; “memory” signifies incremented or decremented memory addresses.

Note 2: The transfer mode register should not be set to any value other than those listed above.

Note 3: The execution state number shows number of best case (1-state memory access).