5 serial channel timing, Tmp92cz26a – Toshiba H1 Series User Manual

Page 662

TMP92CZ26A

92CZ26A-659

4.3.5

Serial channel timing

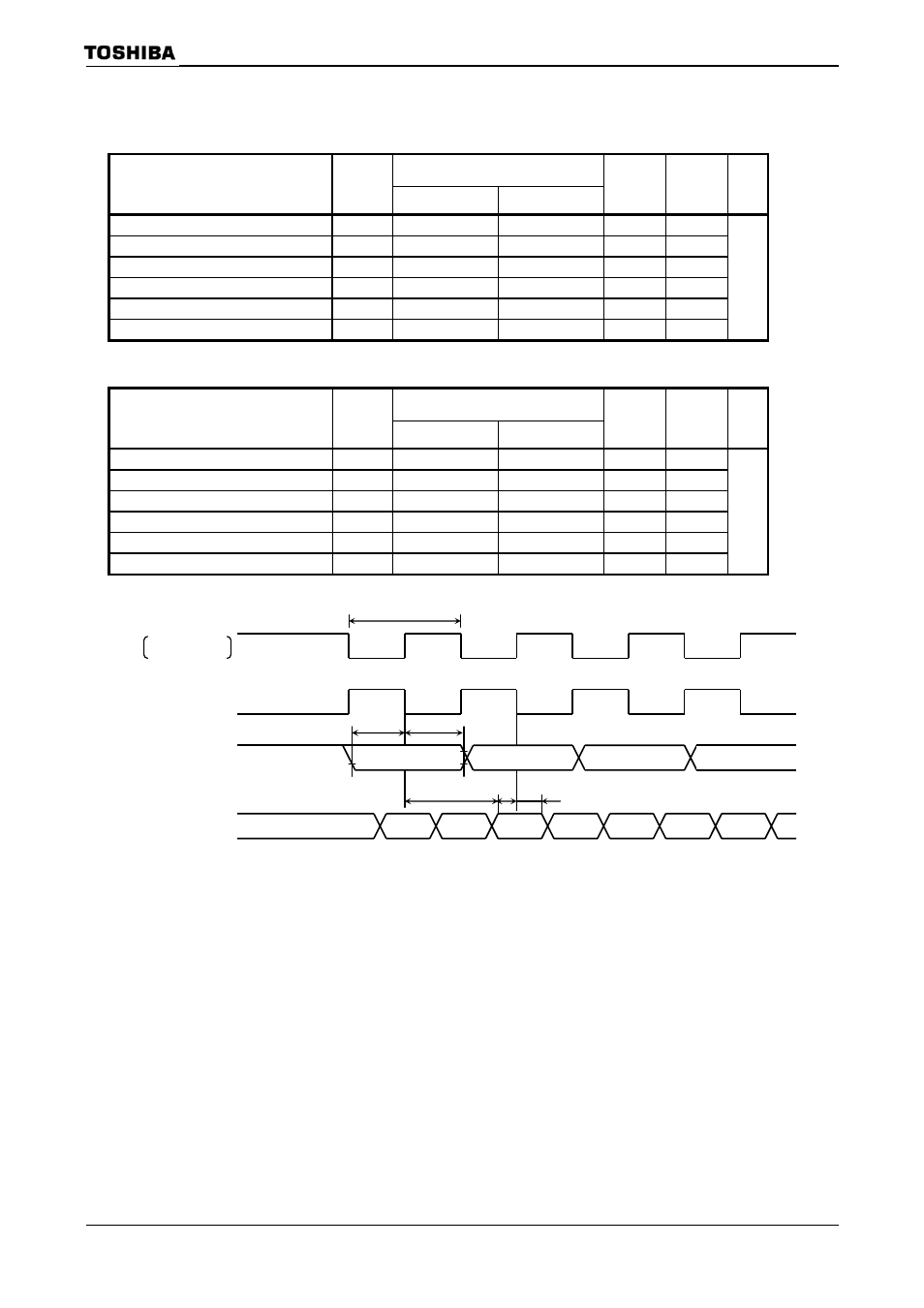

(1) SCLK input mode (I/O interface mode)

Variable

Parameter Symbol

Min Max

80 MHz 60 MHz Unit

SCLK cycle

t

SCY

16T

200

266

Output data

→ SCLK rising/ falling

t

OSS

t

SCY

/2

− 4T − 30

20

36.4

SCLK rising/ falling

→ Output data hold

t

OHS

t

SCY

/2

+ 2T -20

105

146

SCLK rising/ falling

→ Input data hold

t

HSR

2T

+ 10

35

43

SCLK rising/ falling

→ Input data valid

t

SRD

t

SCY

− 20

180 246

Input data valid

→ SCLK rising/ falling

t

RDS

20

20

20

ns

(2) SCLK output mode (I/O interface mode)

Variable

Parameter Symbol

Min Max

80 MHz 60 MHz Unit

SCLK cycle (Programmable)

t

SCY

16T 8192T

200

266

Output data

→ SCLK rising/ falling

t

OSS

t

SCY

/2

− 40

60

93

SCLK rising/ falling

→ Output data hold

t

OHS

t

SCY

/2

− 40

60

93

SCLK rising/ falling

→ Input data hold

t

HSR

0

0

0

SCLK rising/ falling

→ Input data valid

t

SRD

t

SCY

− 1T − 50

137.5 199

Input data valid

→ SCLK rising/ falling

t

RDS

1T

+ 50

62.5

66

ns

t

SCY

Input data

RXD

0

SCLK

Output mode/

Input mode

SCLK

(Input mode)

Output data

TXD

1

2

3

t

OSS

t

OHS

0

1

2

3

t

SRD

t

RDS

t

HSR

Valid

Valid

Valid

Valid