Toshiba H1 Series User Manual

Page 484

TMP92CZ26A

92CZ26A-481

(h)

This bit is for Software reset of transmit/receive FIFO pointer. Write SPICT

“0” at

read/write pointer of transmit/receive FIFO are initialized.

When writing SPICT

transmitting is transmitted. Write

becomes to invalid.

The data in the transmit shift register is cleared simultaneously. Therefore, the data is

not output if transmit is restarted after executed software reset.

Please do not write

received data in the receive FIFO buffer becomes invalid. However, the UNIT data in

receiving is loaded to receive FIFO as valid data.

In case of sequential receive, receiving operates sequentially even if the data of receive

buffer becomes invalid. Therefore, stops receive operation by writing

SPICT

operation is stopped by writing

(namely after REND interrupt or the time to receive 1UNIT).

During receiving, do not write

Software reset can be executed by 1 shot operation; writing

write

(i)

Enable/disable control of root clock this SPI controller.

(j)

Select baud rate. Baud rate is created from f

SYS

and settings are in under table.

Please change the setting when transmitting/receiving are not in operation.

Note: When setting the baud rates, select less than 20Mbps according to the operation speed of CPU (f

SYS

).

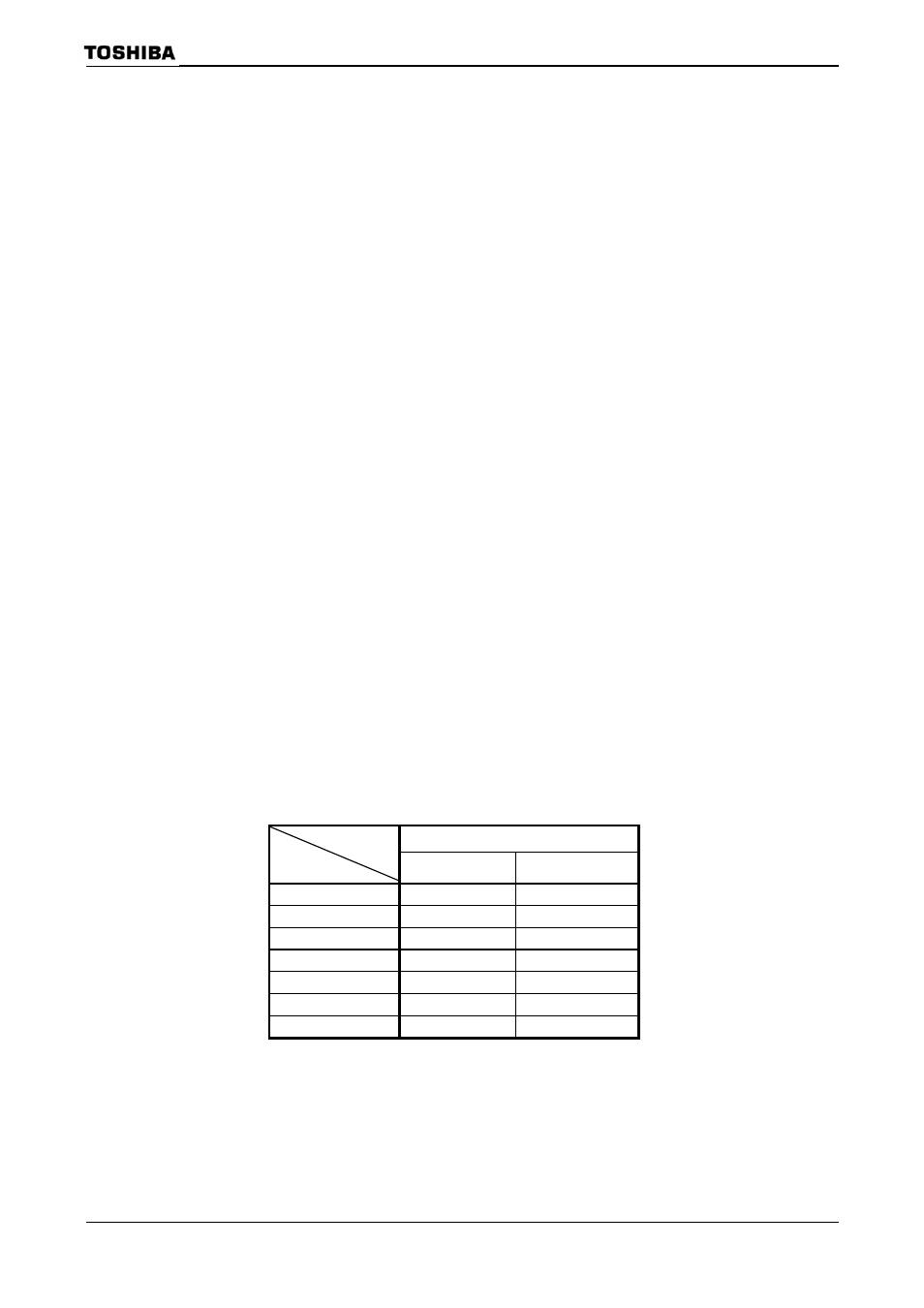

Table 3.17.1 Example of Baud Rate

Baud Rate [Mbps]

f

SYS

=60MHz

f

SYS

=80MHz

f

SYS

/2

−

−

f

SYS

/3

20

−

f

SYS

/4

15 20

f

SYS

/8

7.5 10

f

SYS

/16

3.75 5

f

SYS

/64

0.9375 1.25

f

SYS

/256

0.234375 0.3125