Toshiba H1 Series User Manual

Page 251

TMP92CZ26A

92CZ26A-248

(i)

The

this bit should be set to “0”.

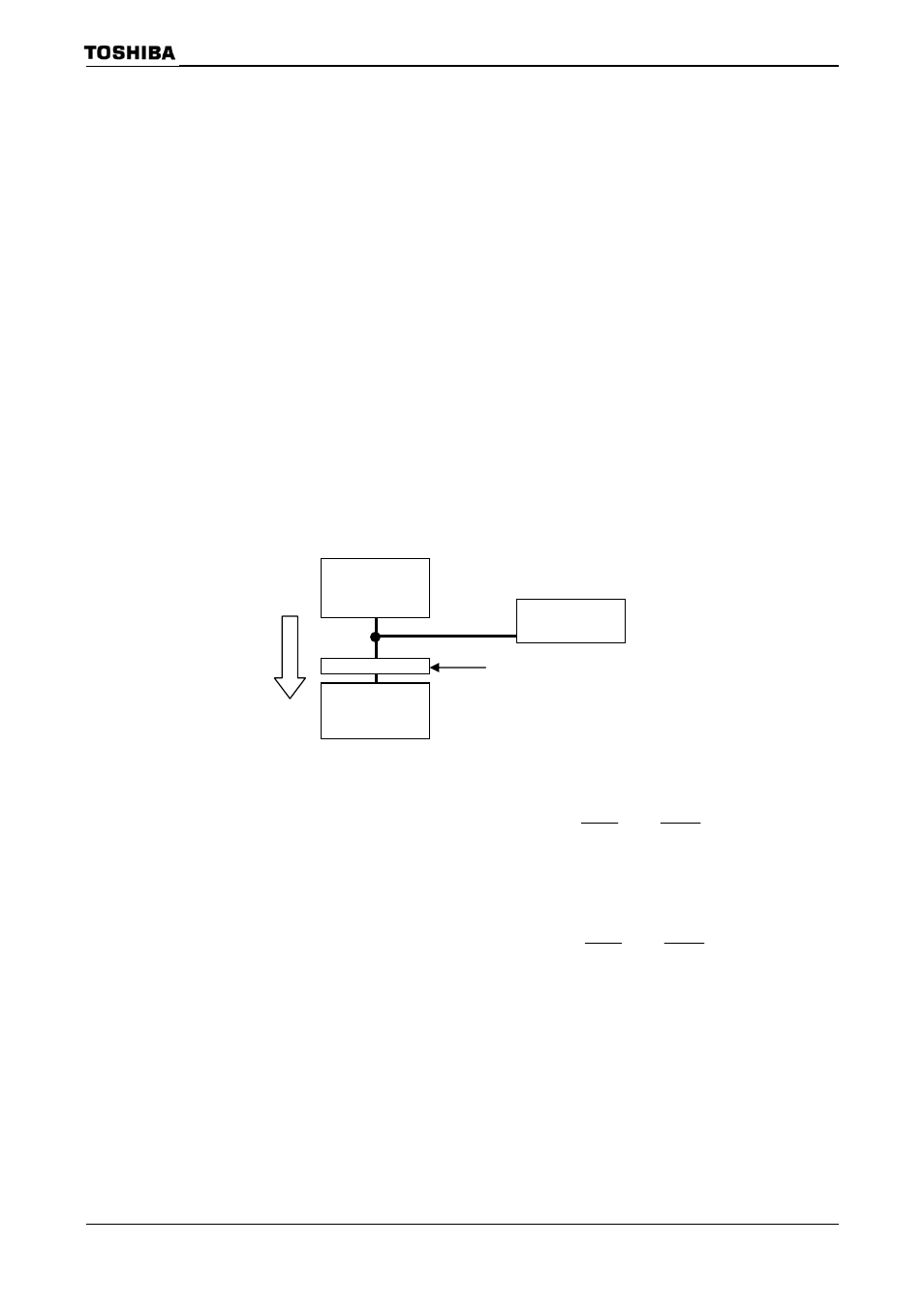

The Reed-Solomon processing unit is comprised of two elements: an ECC generator and

an ECC calculator. The latter is used to calculate the error address and error bit position.

The error address and error bit position are calculated using an intermediate code

generated from the ECC for written data and the ECC for read data. At this time, no special

care is needed if ECC generation and error calculation are performed serially. If these

operations need to be performed parallely, the intermediate code used for error calculation

must be latched while the calculation is being performed. The

enable this latch operation.

When

generator can generate the ECC for another page without problem while the ECC

calculator is calculating the error address and error bit position. At this time, the ECC

generator can perform both encode (write) and decode (read) operations.

When

calculator are updated as the data in the ECC generator is updated.

(j)

The

These bits are used to specify the High width of the

NDRE

and

NDWE

signals. The High

width to be inserted is obtained by multiplying the value set in these bits by f

SYS.

(k)

The

These bits are used to specify the Low width of the

NDRE

and

NDWE

signals. The Low

width to be inserted is obtained by multiplying the value set in these bits by f

SYS.

Reed-Solomon

ECC

Generator

Reed-Solomon

ECC

Calculator

F/F 80bit

NDECCRDn

Register

Flow of data