Tmp92cz26a – Toshiba H1 Series User Manual

Page 649

TMP92CZ26A

92CZ26A-646

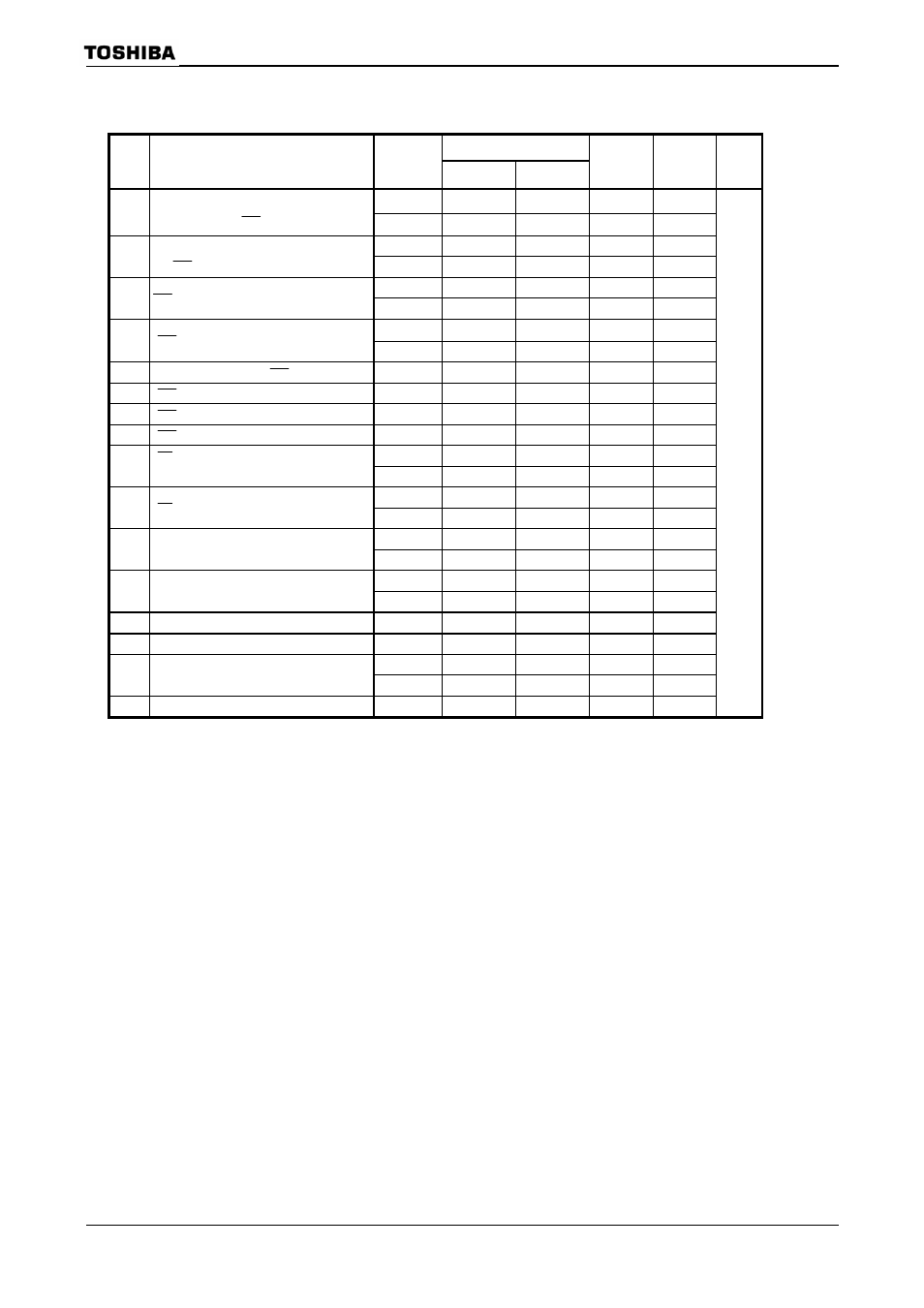

Write cycle

Variable

No. Parameter Symbol

Min Max

80MHz 60MHz Unit

t

DW

1.0T

− 10.0

−

6.6

16-1

D0 ~ D15 valid

→

WR

xx rising at 0 waits

t

DW

1.0T

− 6.0

6.5

−

t

DW4

3.0T

− 10.0

−

39.8

16-2

D0 ~ D15 valid

→

WR

xx rising at 2 waits/4 waits

t

DW6

5.0T

− 6.0

56.5

−

t

WW

1.0T

− 7.0

−

9.6

17-1

WR

xx low width at 0 waits

t

WW

1.0T

− 4.0

8.5

−

t

WW4

3.0T

− 7.0

−

42.8

17-2

WR

xx low width at 2 waits/4 waits

t

WW6

5.0T

− 4.0

58.5

−

18 A0 ~ A23 valid →

WR

falling

t

AW

0.5T

− 5.0

1.25

3.3

19

WR

xx falling

→ SDCLK rising

t

WK

0.5T

− 5.0

1.25

3.3

20

WR

xx rising

→ A0 ~ A23 hold

t

WA

0.5T

− 5.0

1.25

3.3

21

WR

xx rising

→ D0 ~ D15 hold

t

WD

0.5T

− 5.0

1.25

3.3

t

RDO

0.5T

− 2.0

−

6.3

22-1

RD

rising

→ D0 ~ D15 output

t

RDO

0.5T

− 1.0

5.25

−

t

RDO

1.5T

− 2.0

−

22.9

22-2

RD

rising

→ D0 ~ D15 output

t

RDO

2.5T

− 1.0

30.25

−

t

SWP

1.0T

− 7.0

−

9.6

23 Write width for SRAM

t

SWP

1.0T

− 4.0

8.5

−

t

SBW

1.0T

− 7.0

−

9.6

24

Data byte control ~ end of write

for SRAM

t

SBW

1.0T

− 4.0

8.5

−

25 Address setup time for SRAM

t

SAS

0.5T

− 5.0

1.25

3.3

26 Write recovery time for SRAM

t

SWR

0.5T

− 5.0

1.25

3.3

t

SDS

1.0T

− 10.0

−

6.6

27 Data setup time for SRAM

t

SDS

1.0T

− 6.0

6.5

−

28 Data hold time for SRAM

t

SDH

0.5T

− 5.0

1.25

3.3

ns

AC measuring condition

Note:

The operation guarantee Temperature: 80MHz: Ta=0

∼50°C, less than 60MHz: Ta=0∼70°C