3 detailed description of timing – Toshiba H1 Series User Manual

Page 627

TMP92CZ26A

92CZ26A-624

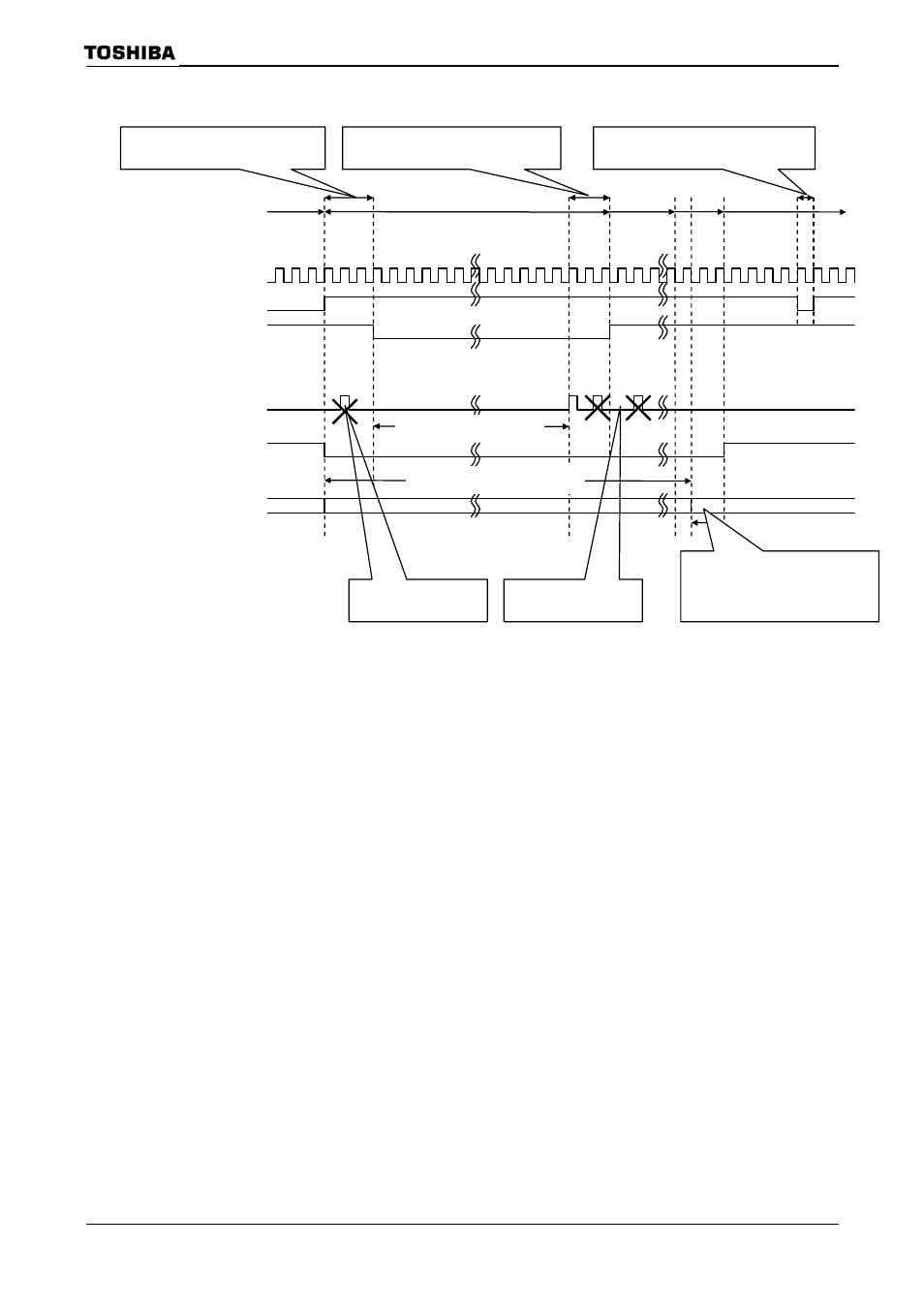

3.25.3 Detailed Description of Timing

Internal HOT_RESET assert to dead circuit only. (DVCC1A &DVCC1C circuit)

1. If it is set PMCCTL

3-clock times maximum (around 92

μS) to shift from normal mode to Power Cut Mode.

And the wake-up triggers during this 3-clock times, are ignored.

2. It spends 2.5-clock times maximum (around 77

μS) from the trigger to wake-up to rise-up

the PWE terminal.

3. After wake-up from Power Cut Mode, reset to "0" the PMCCTL

ware. If you want to shift Power Cut Mode again, need to wait 1-clock time minimum

(around 31

μS).

4. The wake-up triggers during waking-up, are ignored.

5. After Warm-up count, and spend 1-clock time (around 31

μS), release the DRV setting of

every ports. After that, spends 2-clock time (around 62

μS), release internal RESET

(Hot_Reset).

CPU state transition

PMCCTL

PWE pin

INTRTC

INT0-7, INTKEY

Internal HOT_RESET

Port state

XT2

1. A maximum of 3 clocks (92

μs)

are needed for entering PCM.

Normal Power Cut Mode (PCM) Warm-up 3CLK Normal

2. A maximum of 2.5 clocks (77

μs)

are needed from interrupt request.

4. These interrupts

are ignored.

3. A minimum of 1 clock (31

μs) is

needed for entering PCM again.

Interrupt enabled period

1. This interrupt is

ignored.

5. The drive register setting is

released a maximum of 1 clocks

(31

μs) after the end of warm-up.

Drive register active period