2 operation – Toshiba H1 Series User Manual

Page 300

TMP92CZ26A

92CZ26A-297

3.13.2 Operation

(1) Prescaler

The 5-bit prescaler generates the source clock for TMRB0. The prescaler clock (

φT0)

is selected by the register SYSCR0

started or stopped using TB0RUN

set to “1”; the prescaler is cleared to “0” and stops operation when

cleared to “0”.

The resolution of prescaler is showed in the Table 3.13.2.

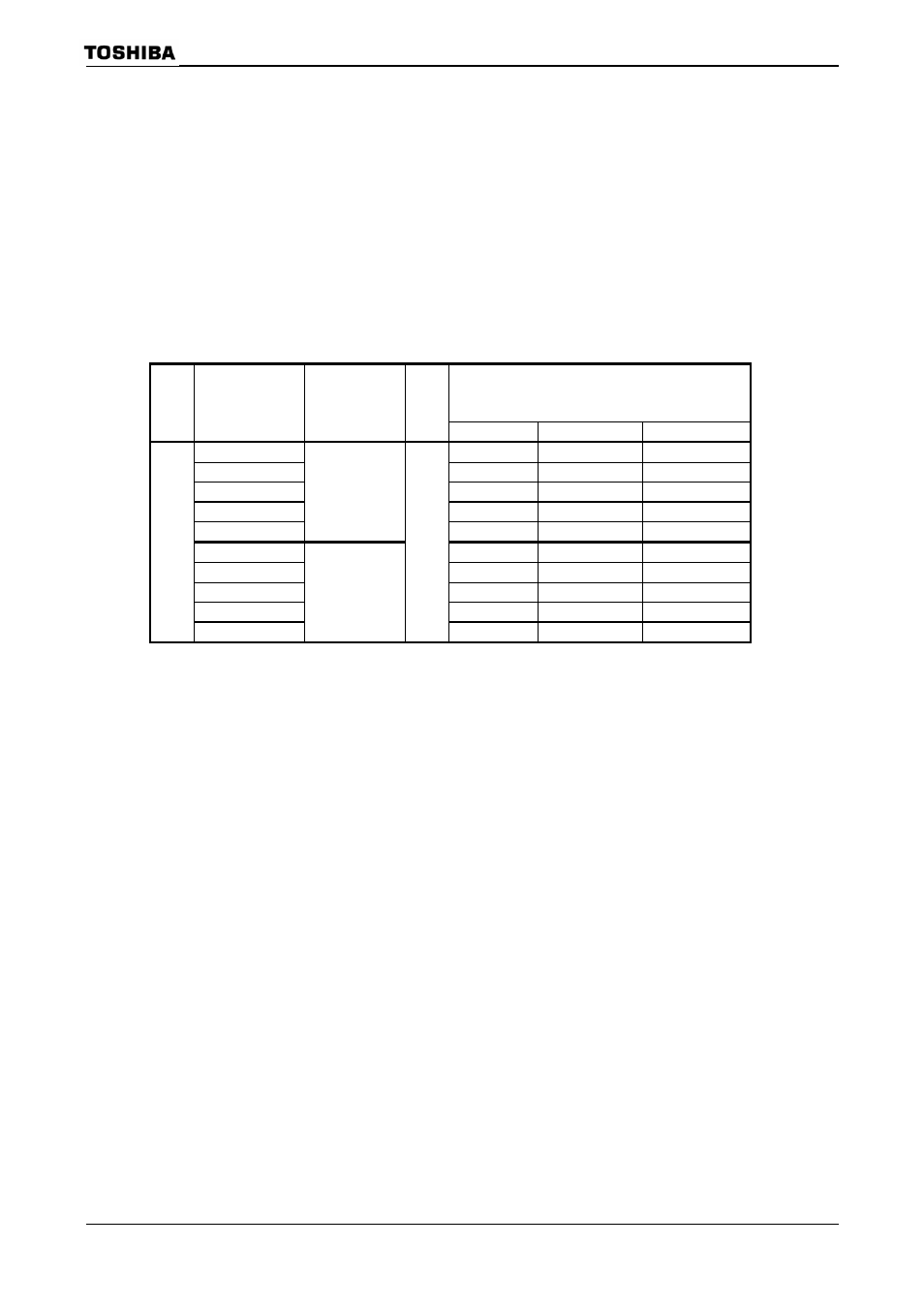

Table 3.13.2 Prescaler Clock Resolution

Timer counter input clock

Prescaler of TMRB

TBxMOD

Clock

gear

selection

SYSCR1

Prescaler of

clock gear

SYSCR0

−

φT1(1/2)

φT4(1/8)

φT16(1/32)

1/1 fc/8

fc/32

fc/128

1/2 fc/16

fc/64

fc/256

1/4 fc/32

fc/128

fc/512

1/8

fc/64

fc/256

fc/1024

1/16

1/2

fc/128

fc/512

fc/2048

1/1 fc/32

fc/128

fc/512

1/2 fc/64

fc/256

fc/1024

1/4 fc/128

fc/512

fc/2048

1/8 fc/256

fc/1024

fc/4096

fc

1/16

1/8

1/2

fc/512

fc/2048

fc/8192

(2) Up counter (UC10)

UC10 is a 16-bit binary counter which counts up pulses input from the clock

specified by TB0MOD

Any one of the prescaler internal clocks

φT1, φTB0 and φT16 or an external clock

input via the TB0IN0 pin can be selected as the input clock. Counting or stopping and

clearing of the counter is controlled by TB0RUN

When clearing is enabled, the up counter UC10 will be cleared to zero each time its

value matches the value in the timer register TB0RG1H/L. Clearing can be enabled or

disabled using TB0MOD

If clearing is disabled, the counter operates as a free running counter.