Toshiba H1 Series User Manual

Page 111

TMP92CZ26A

92CZ26A-108

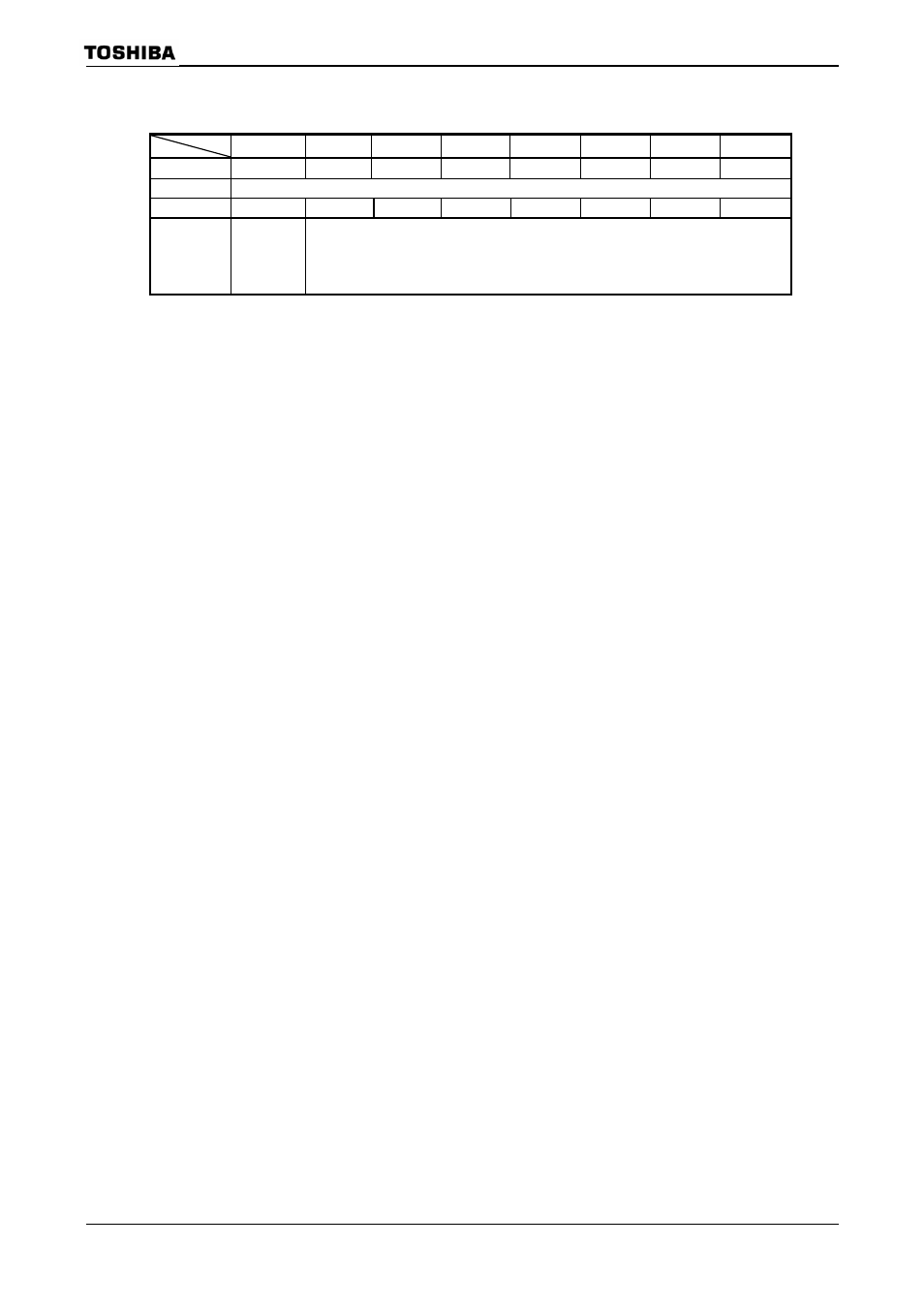

HDMATR Register

7 6 5 4 3 2 1 0

bit Symbol

DMATE

DMATR6

DMATR5

DMATR4

DMATR3

DMATR2

DMATR1 DMATR0

Read/Write R/W

After reset

0

0

0

0

0

0

0

0

Function

Timer

operation

0: Disable

1: Enable

Maximum bus occupancy time setting

The value to be set in

“maximum bus occupancy time / (256/fSYS)”.

“00H” cannot be set.

Note: Read-modify-write instructions can be used on this register.

By writing “87H” to the HDMATR register, the maximum HDMA time is set to 29.9 [

μs]

(256

Ч 7 Ч (1 / f

SYS

)). Since HDMA start interval [period:s] = 83.33 [ms] is longer than

LHSYNC

[period:s] = 54.95 [

μs], it is assumed that HDMA transfer occurs once during

LHSYNC

[period:s].

Since SDRAM is auto-refreshed once or less in 5.47 [

μs]:

t

STOP

(ARDMA)

= 2 / f

SYS

[Hz]

= 33.33 [ns]

The time LDMA, ARDMA, and HDMA all occupy the bus is defined as:

t

STOP

(LDMA ARDMA HDMA)

Based on the above, the CPU bus stop rate is calculated as follows:

CPU bus stop rate

= t

STOP

(LDMA ARDMA HDMA) [s] / LHSYNC

[period:s]

= (5.47 [μs] + 33.33 [ns]+29.9 [μs]) / 54.95 [μs] = 64.42 [%]

Note: To be precise, the bus assert time and RAM access time are added each time the HDMA transfer time is

forcefully terminated at 29.9 [

μs].

HDMATR

(097FH)