1 block diagram – Toshiba H1 Series User Manual

Page 298

TMP92CZ26A

92CZ26A-295

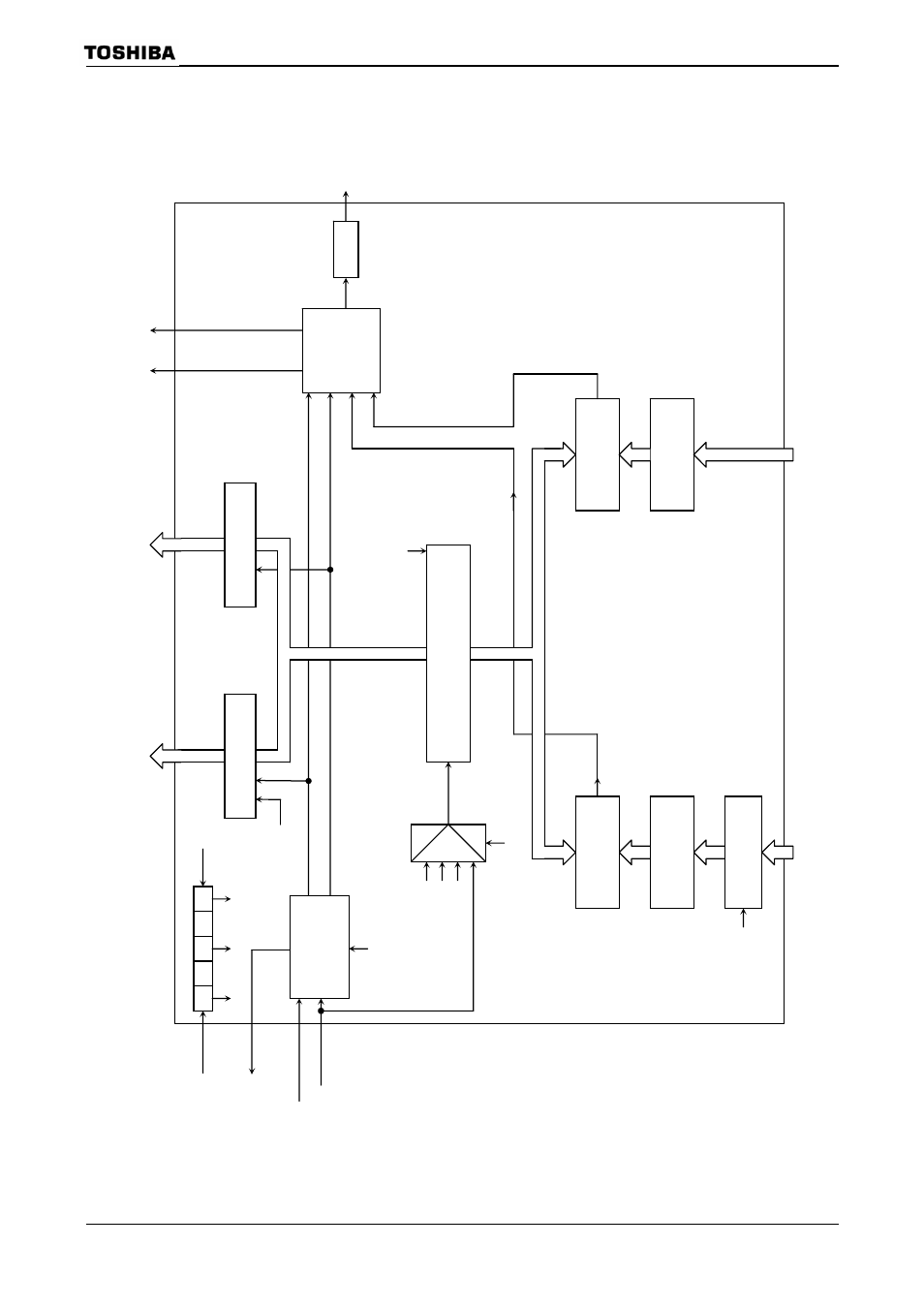

3.13.1 Block diagram

Figure 3.13.1 Block diagram of TMRB0

Internal data bus

Slelector

16-bit comparato

r

(CP10)

TB0MOD

φT1

φT4

φT16

Ti

mer

flip-

flop

control

TB0FF

0

TB0OUT0

Match

detection

16-bit timer regis

ter

TB0R

G0H/L

Register buffer

1

0

TA1O

UT

TB1MO

D

16-bit time register

TB0R

G1H/L

TB0MO

D

16-bit comparato

r

(CP11)

Capture,

external interrupt

input control

TB0RUN<

TB0R

UN>

Caputure registe

r

1

TB0CP1H/L

Capture register 0

TB0CP0H/L

Run/

clear

Internal data bus

Match detection

16-bit up counter

(UC10

)

Count

clock

(from TMRA01

)

Pr

escaler

clock

φT0

TMR

32

16

8

4

2

φT1

φT4

φT16

TB0RUN

Internal data bus

TB0MOD

Intenal data bus

Ti

me

r

flip-

flop

Ti

mer fl

ip

-fl

op

output

Interrup

t output

register 0

INTTB00

register 1

INTTB01

TB0RUN

External INT

in

put

INT6

TB0IN0