Toshiba H1 Series User Manual

Page 356

TMP92CZ26A

92CZ26A-353

(6)

Transmitter/Receiver selection

Set the SBICR2

Clear the

In Slave Mode,

z

Data with an addressing format is transferred

z

A slave address with the same value that an I2CAR

z

A GENERAL CALL is received (all 8-bit data are “0” after a start condition)

The

W

R/

) sent from the

master device is “1”, and is cleared to “0” by the hardware if the bit is “0”.

In the Master Mode, after an Acknowledge signal is returned from the slave device,

the

set to “1” by the hardware if it is “0”. When an Acknowledge signal is not returned, the

current condition is maintained.

The

2

C bus is

detected or arbitration is lost.

(7)

Start/Stop condition generation

When the SBISR

SBIDBR are output on a bus after generating a start condition by writing “1” to the

SBICR2

buffer register (SBIDBR) and set “1” to

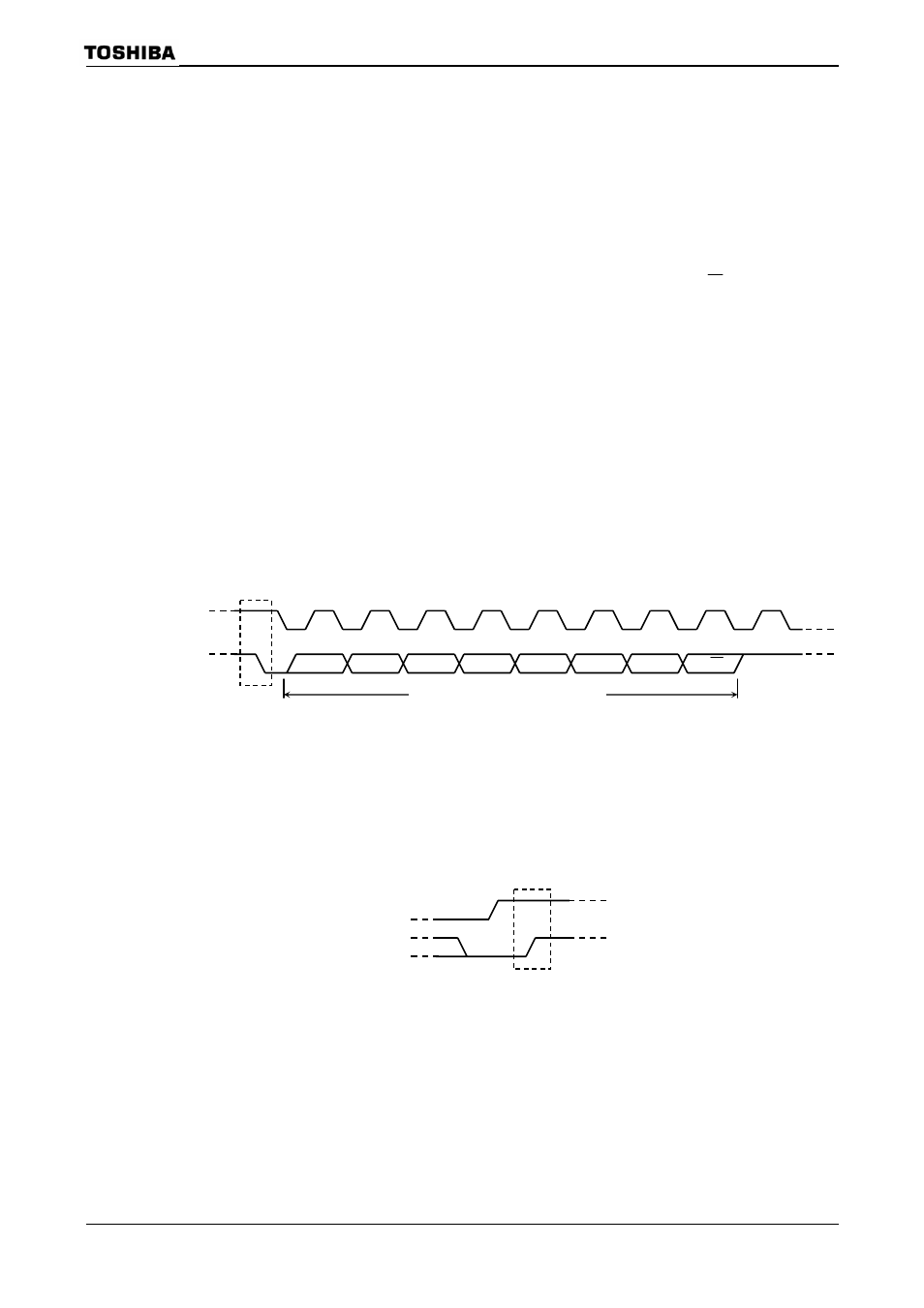

Figure 3.15.10 Start condition generation and slave address generation

When the

writing “1” to the

of

Figure 3.15.11 Stop condition generation

The state of the bus can be ascertained by reading the contents of SBISR

SBISR

be cleared to 0 if a stop condition has been detected.

SCL pin

Start condition

A6

Slave address and the direction bit

Acknowledge

signal

1

SDA pin

2

3

4

5

6

7

8

9

A5

A4

A3

A2

A1

A0

R/ W

Stop condition

SCL pin

SDA pin