Toshiba H1 Series User Manual

Page 608

TMP92CZ26A

92CZ26A-605

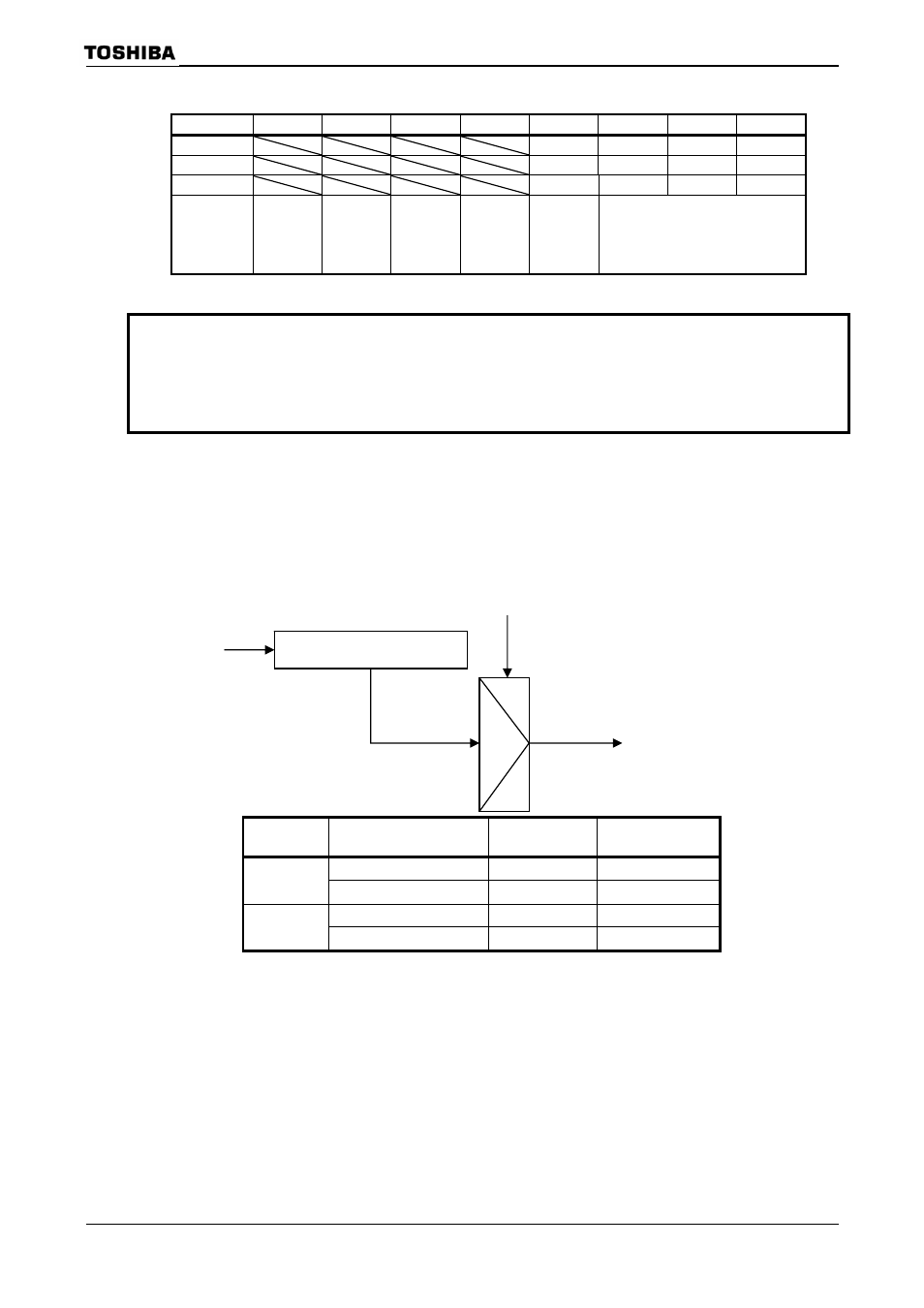

AD Conversion Clock Setting Register

7 6 5 4 3 2 1 0

bit

Symbol

−

ADCLK2 ADCLK1 ADCLK0

Read/Write

R/W

R/W

R/W

R/W

After

reset

0

0

0

0

Function

Always

write “0”

Select clock for AD conversion

000 : Reserved 100 : f

IO

/4

001 : f

IO

/1 101 : f

IO

/5

010 : f

IO

/2 110 : f

IO

/6

011 : f

IO

/3 111 : f

IO

/7

Note1: AD conversion is executed at the clock frequency selected in the above register. To assure

conversion accuracy, however, the conversion clock frequency must not exceed 12MHz

MHz.

Note2: Don ‘t change the clock frequency while AD conversion is in progress.

Figure 3.23.11 AD Conversion Registers

f

IO

(f

SYS

/2)

AD conversion

speed

100(f

IO

/4)

10.0MHZ

12

μsec

40MHz

101(f

IO

/5)

8MHZ

15

μsec

011(f

IO

/3)

10.0MHZ

12

μsec

30MHz

100(f

IO

/4)

7.5MHZ

16

μsec

AD conversion speed can be calculated by following.

Conversion speed

= 120 × (1/ADCLK)

ч1 ∼ ч7

f

SYS

ADCLK

ADCCLK

(12BFH)