Toshiba H1 Series User Manual

Page 528

TMP92CZ26A

92CZ26A-525

•

Setting method

The front dummy LHSYNC (vertical front porch) not accompanied by valid data in

the total of LHSYNC period in the LVSYNC period is defined by the value set in

LCDPRVSP

Front dummy LHSYNC (vertical front porch) =

The back dummy LHSYNC (vertical back porch) is defined as follows:

(

+ 1) − (valid LHSYNC: common size) − (front dummy LHSYNC:

The vertical back porch must have a minimum of one dummy clock.

The front dummy LCP0 (horizontal front porch) not accompanied by valid data in the

total number of LCP0 clocks in the LHSYNC period is defined by the value set in

LCDLDDLY

Front dummy LCP0 (horizontal front porch) =

The back dummy LCP0 (horizontal back porch) is defined as follows:

(

− (valid LCP0: segment size) − (front dummy LCP0:

Note 1: The back dummy LCP0 (horizontal back porch) must have a minimum of two LCP0 clocks.

Note 2: The delay time that is set in LCDLDDLY

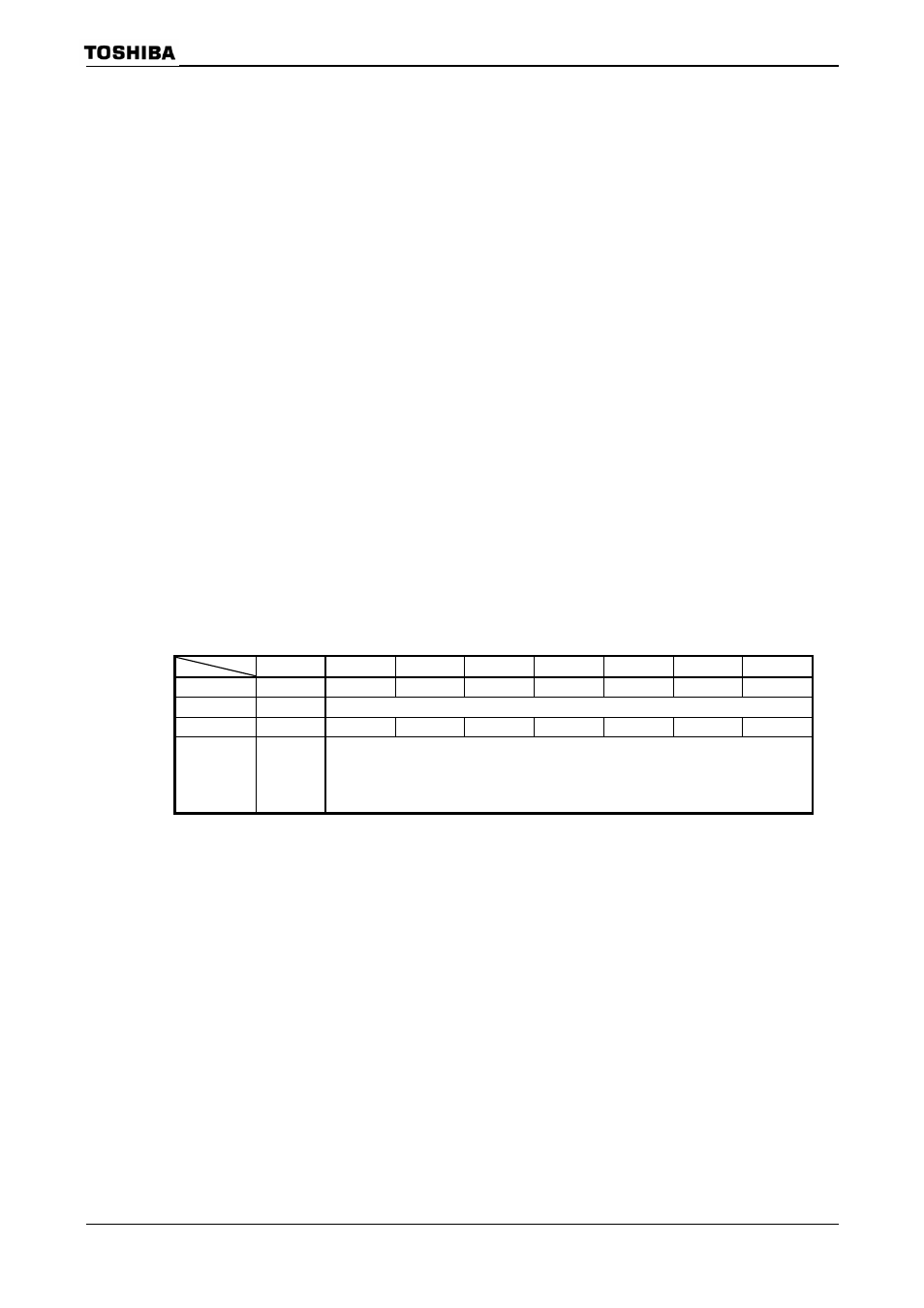

7 6 5 4 3 2 1 0

bit

Symbol PDT LDD6 LDD5 LDD4 LDD3 LDD2 LDD1 LDD0

Read/Write R/W

W

After

reset

0 0 0 0 0 0 0 0

Function

Data output

timing

0: Sync with

LLOAD

1: 1 clock later

than LLOAD

LLOAD delay (bits 6-0)

Example 1) Setting the refresh rate to 200 Hz under the following conditions:

f

SYS

= 30 MHz, STN mode, 320-segment × 240-common, 4096-color display,

LCDMODE0

Internal reference clock LCP0 = f

SYS

/ 4 = 30 [MHz] / 4 = 7.5 [MHz]

Therefore, LCP0 period = 1 / 7.5 [MHz] = 0.133 [

μS]

Condition 1: Refresh rate = 200 Hz, Refresh cycle = 5 [ms

Condition 2: LH =

≥ (320×3/8) − 1 = 119

Condition 3: LV =

≥ 240 − 1

When

LVSYNC [s: period]

= LHSYNC [s: period] × (

= LCP0 [s: period] × (

5

[ms]

= (1 / 7.5 [MHz]) × (LH + 1) ×240

LH

+ 1

= (5 Ч 10

-3

)

Ч (7.5 Ч 10

6

) / 240

= 156.25

LCDLDDLY

(0290H)