Table 5-95, Telecom clock monitor time base register, Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 168

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

168

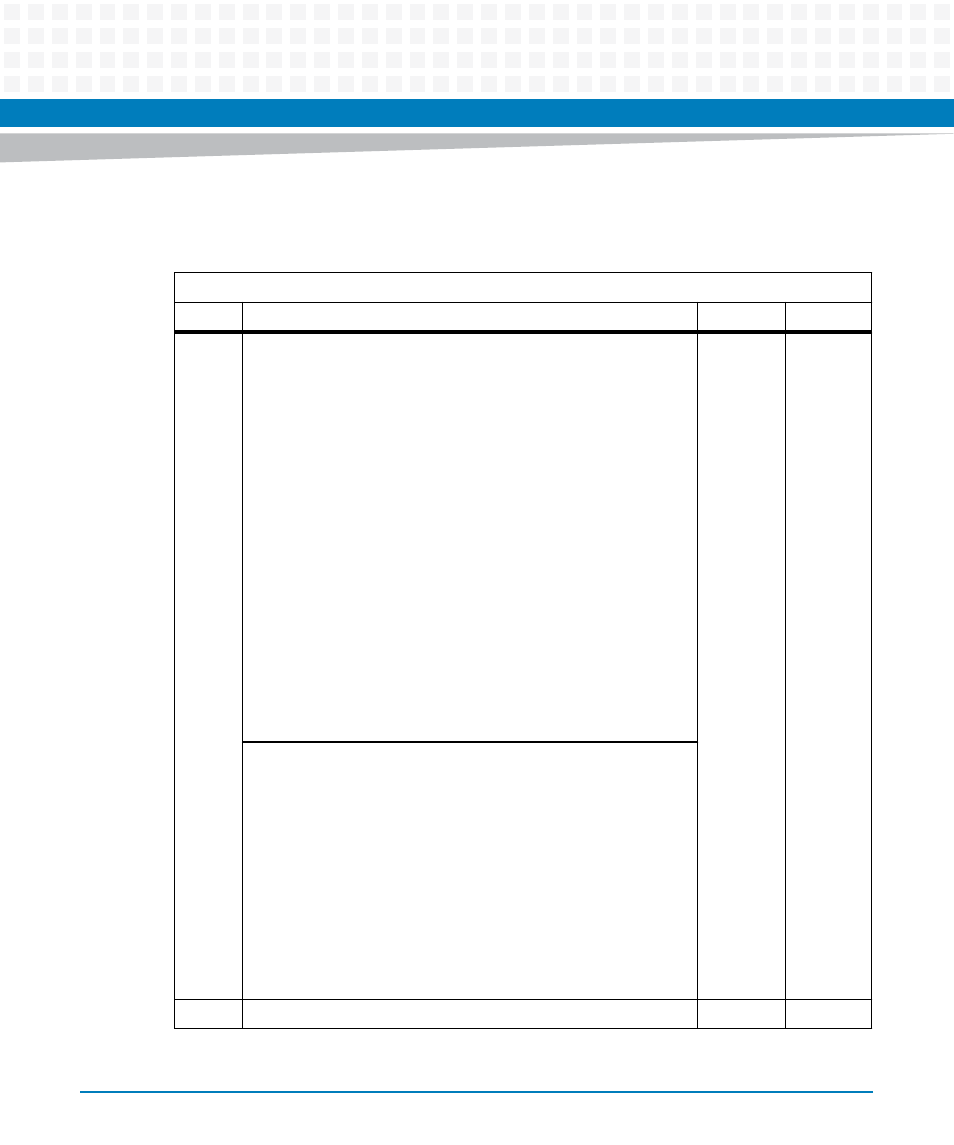

Table 5-95 Telecom Clock Monitor Time Base Register

Address: 0x64

Bit

Description

Default

Access

4:0

Select Time base for clock supervision with Gate Mode:

0: Gate is open for 250 us

1: Gate is open for 500 us

2: Gate is open for 1ms

3: Gate is open for 2ms

4: Gate is open for 4ms

5: Gate is open for 8ms

6: Gate is open for 16ms

7: Gate is open for 32ms

8: Gate is open for 64ms

9: Gate is open for 128ms

10: Gate is open for 256ms

11: Gate is open for 512ms

12: Gate is open for 1024ms

13: Gate is open for 2048ms

14: Gate is open for 4096ms

15: Gate is open for 8192ms

16: Gate is open for 16384ms

17 and all others: Gate is open for 32768ms

0

LPC: r/w

Select Time base for clock supervision with Period Mode:

0: Period Counter incremented with each master clock

1: Period Counter incremented with each 2nd master clock

2: Period Counter incremented with each 4th master clock

3: Period Counter incremented with each 8h master clock

4: Period Counter incremented with each 16th master clock

5: Period Counter incremented with each 32th master clock

6: Period Counter incremented with each 64th master clock

7: Period Counter incremented with each 128th master clock

8: Period Counter incremented with each 256th master clock

9 and all others: Period Counter incremented with each 512th master

clock

6:5

Reserved

0

r