3 super io configuration register, 1 entering the configuration state, 2 existing the configuration state – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 102: Table 5-6, Super io configuration index register, Table 5-7, Super io configuration data register, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

102

5.1.3

Super IO Configuration Register

After an LPC Reset (PCH_PLTRST_ is asserted) or “Power On Reset” the Super IO is in the Run

Mode with the UARTs disabled. They may be configured using the LPC IO Address Range SIW

(INDEX and DATA) by placing the Super IO into Configuration Mode. The BIOS uses these

configuration addresses to initialize the logical devices at POST. The INDEX and DATA

addresses are only valid when the Super IO is in Configuration State. The INDEX and DATA

addresses are effective only when the Super IO is in the Configuration State. When the Super

IO is not in the Configuration State, reads return 0xFF and write data is ignored.

5.1.3.1

Entering the Configuration State

The device enters the Configuration State by the following contiguous sequence:

1. Write 80H to Configuration Index Port.

2. Write 86H to Configuration Index Port.

5.1.3.2

Existing the Configuration State

The device exits the Configuration State by the following contiguous sequence:

1. Write 68H to Configuration Index Port.

2. Write 08H to Configuration Index Port.

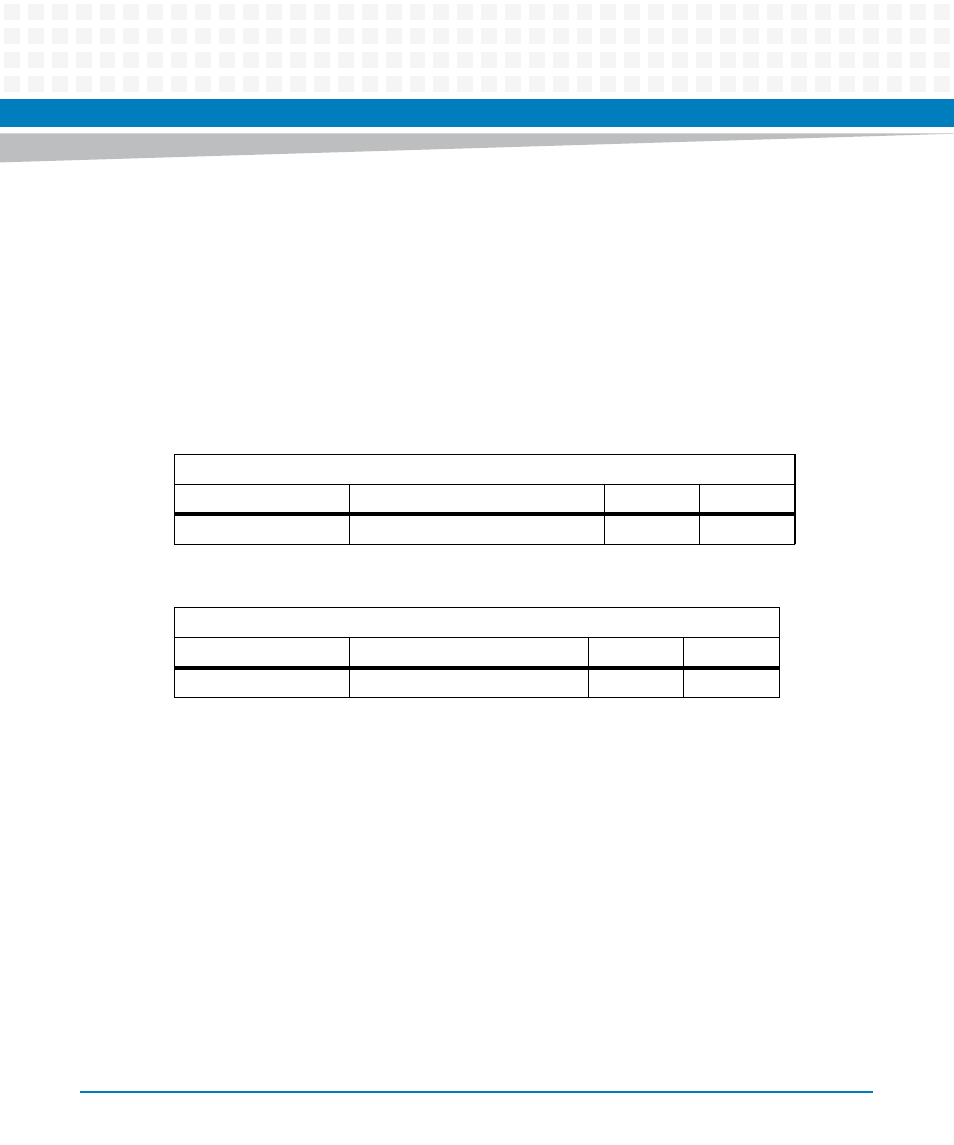

Table 5-6 Super IO Configuration Index Register

LPC I/O Address: 0x4E

Bit

Description

Default

Access

7:0

INDEX. Configuration Index.

0xFF

LPC: r/w

Table 5-7 Super IO Configuration Data Register

LPC I/O Address: 0x4F

Bit

Description

Default

Access

7:0

DATA Configuration Data.

0xFF

LPC: r/w