2 uart registers dlab=0, Table 5-24, Receiver buffer register (rbr) if dlab=0 – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 110: Table 5-23, Maps and registers, 1 receiver buffer register (rbr)

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

110

5.1.4.2

UART Registers DLAB=0

5.1.4.2.1 Receiver Buffer Register (RBR)

In non-FIFO mode, this register holds the character received by the UART's Receive Shift

Register. If fewer than eight bits are received, the bits are right-justified and the leading bits are

zeroed. Reading the register, empties the register and resets the Data Ready (DR) bit in the Line

Status Register to zero. Other (error) bits in the Line Status Register are not cleared. In FIFO

mode, this register latches the value of the data byte at the top of the FIFO.

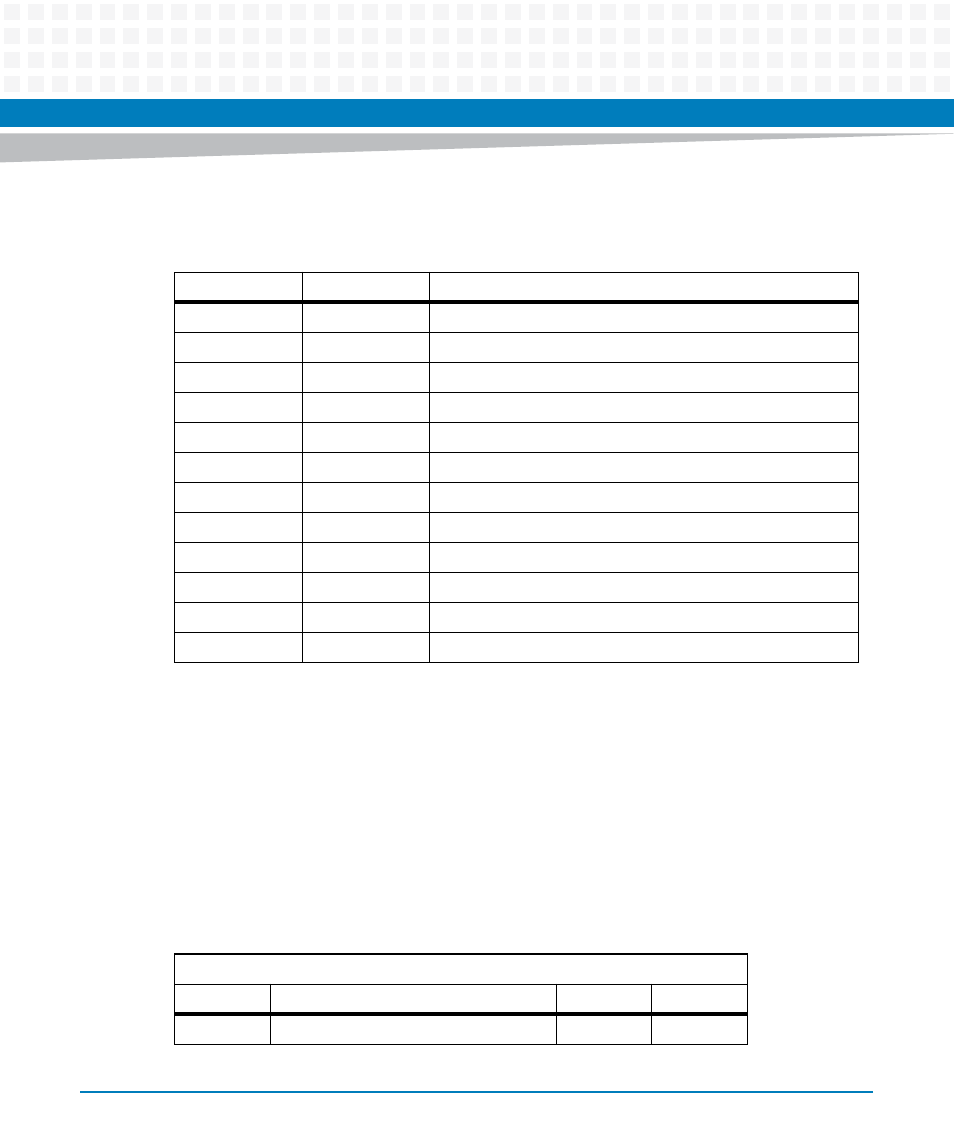

Table 5-23 UART Register Overview

LPC IO Address

DLAB Bit value

Description

Base

0

Receiver Buffer (RBR). Read Only

Base

0

Transmitter Holding (THR). Write Only.

Base + 1

0

Interrupt Enable Register (IER)

Base + 2

X

Interrupt Identification Register (IIR). Read Only

Base + 2

X

FIFO Control Register (FCR). Write Only.

Base + 3

X

Line Control Register (LCR)

Base + 4

X

Modem Control Register (MCR)

Base + 5

X

Line Status Register (LSR). Read Only

Base + 6

X

Modem Status Register (MSR). Read Only

Base + 7

X

Scratch Pad Register (SCR).

Base

1

Divisor Latch LSB (DLL)

Base + 1

1

Divisor Latch MSB (DLM)

Table 5-24 Receiver Buffer Register (RBR) if DLAB=0

LPC IO Address: Base

Bit Description

Default

Access

7:0

Receiver Buffer register (RBR)

Undef.

LPC: r