Table 5-27, Uart interrupt priorities2, Table 5-28 – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 112: Interrupt identification register (iiir), Maps and registers, 4 interrupt identification register (iiir)

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

112

5.1.4.2.4 Interrupt Identification Register (IIIR)

In order to minimize software overhead during data character transfers, the UART prioritizes

interrupts into four levels (listed in Table below) and records these in the Interrupt

Identification Register. The Interrupt Identification Register (IIR) stores information indicating

that a prioritized interrupt is pending and the source of that interrupt.

3

Modem status interrupt enable/disable:

1: modem status interrupt enabled

0: modem status interrupt disabled

0

LPC: r/w

7:4

Reserved

0

LPC: r

Table 5-26 Interrupt Enable Register (IER), if DLAB=0 (continued)

LPC IO Address: Base + 1

Bit Description

Default

Access

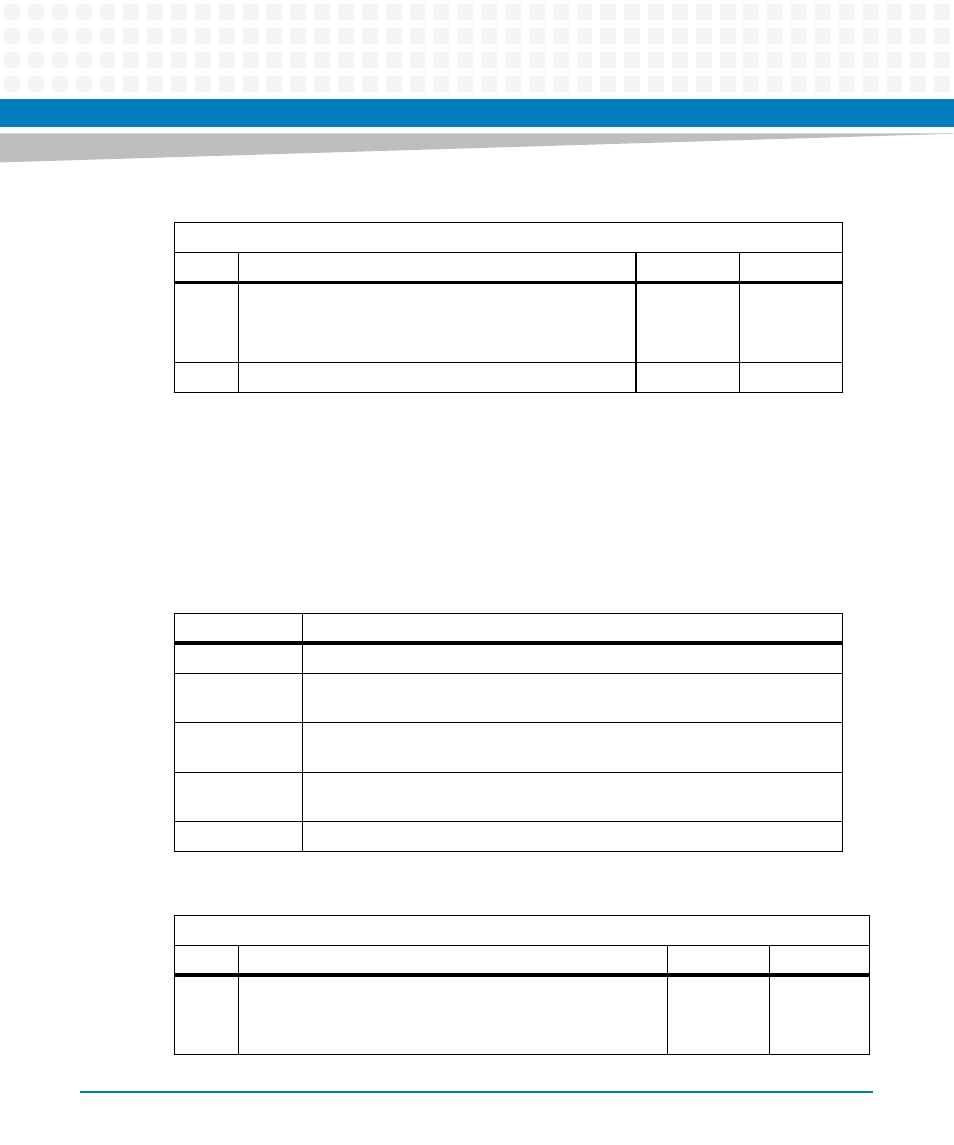

Table 5-27 UART Interrupt Priorities2

Priority Level

Interrupt Source

1 (highest)

Receiver Line Status. One or more error bits were set.

2

Received Data is available. In FIFO mode, trigger level was reached; in non-FIFO

mode, RBR has data.

2

Receiver Time out occurred. It happens in FIFO mode only, when there is data

in the receive FIFO but no activity for a time period.

3

Transmitter requests data. In FIFO mode, the transmit FIFO is half or more than

half empty; in non-FIFO mode, THR is read already

4

Modem Status: one or more of the modem input signals has changed state

Table 5-28 Interrupt Identification Register (IIIR)

LPC IO Address: Base + 2

Bit Description

Default

Access

0

Interrupt status bit:

1: no interrupt pending

0: interrupt pending

1

LPC: r