5 os reset source register, 6 os ipmc watchdog timeout register, Table 5-57 – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 143: Os reset source register, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

143

5.1.12.5 OS Reset Source Register

The OS Reset Source Register stores the source of the most recent reset. It is similar to the BIOS

Reset Source Register. A “1” in the register bit indicates that the associated reset has occurred.

If more than one reset occurs from different sources without clearing the corresponding

register bits, one cannot determine the most recent reset source since more than one bit will

be set. The same will happen if two reset sources go active at the same time.

5.1.12.6 OS IPMC Watchdog Timeout Register

BIOS should never write to this register.

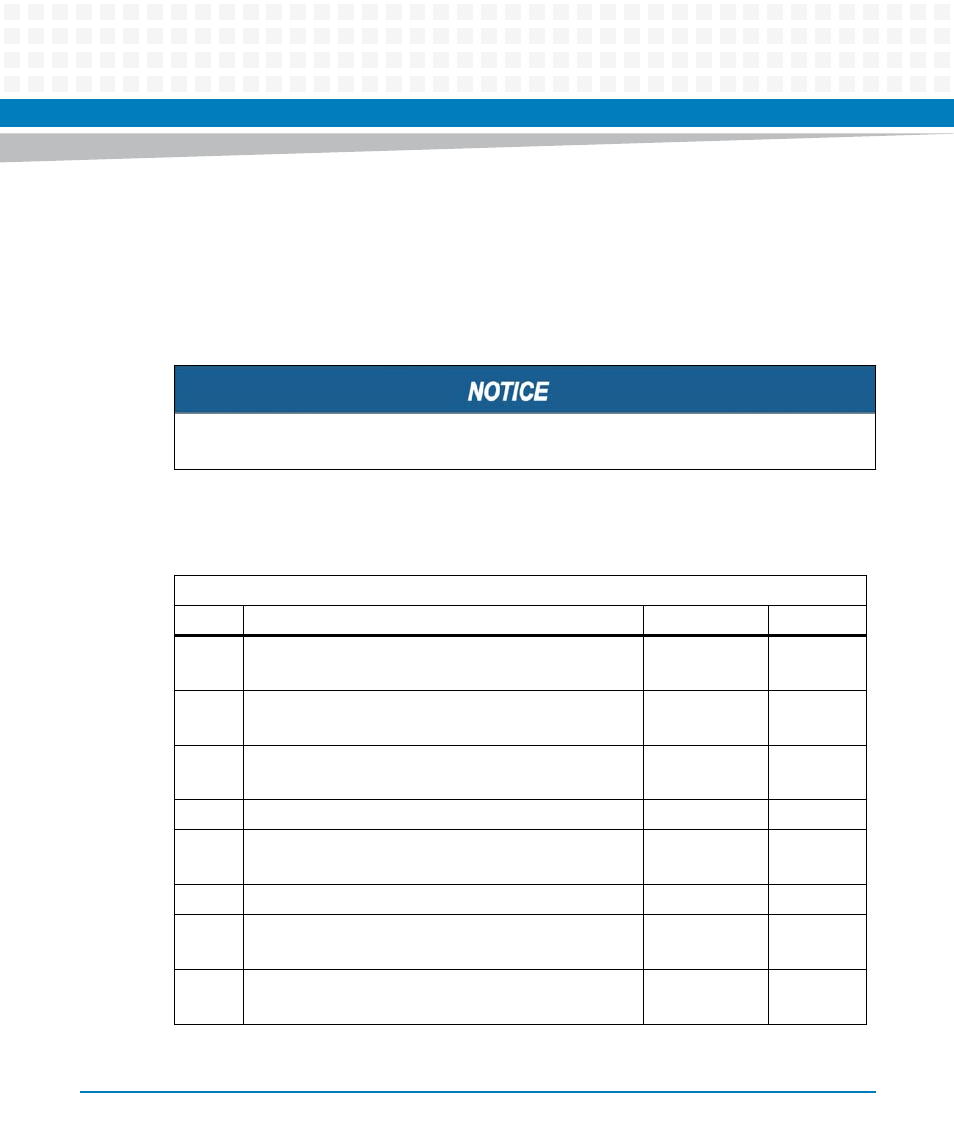

Table 5-57 OS Reset Source Register

Address Offset: 0x14

Bit

Description

Default

Access

0

PWR_GOOD Payload Power-on reset

1: Reset occurred

PWR_GOOD:1

LPC: r/w1c

IPMC: r

1

XDPx reset request (Any one of XDPx signal caused reset

1: Reset occurred

PWR_GOOD:0

LPC: r/w1c

IPMC: r

2

PB_RST_ face plate push button reset

1: Reset occurred

PWR_GOOD:0

LPC: r/w1c

IPMC: r

3

Reserved

0

r

4

RTM_PB_RST_ Reset key at RTM

1: Reset occurred

PWR_GOOD:0

LPC: r/w1c

IPMC: r

5

Reserved

0

r

6

PCH_PLTRST_ reset

1: Reset occurred

PWR_GOOD:0

LPC: r/w1c

IPMC: r

7

IPMC_RST_ REQ_ Payload Reset from IPMC.

1: Reset occurred

PWR_GOOD:0

LPC: r/w1c

IPMC: r