Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 127

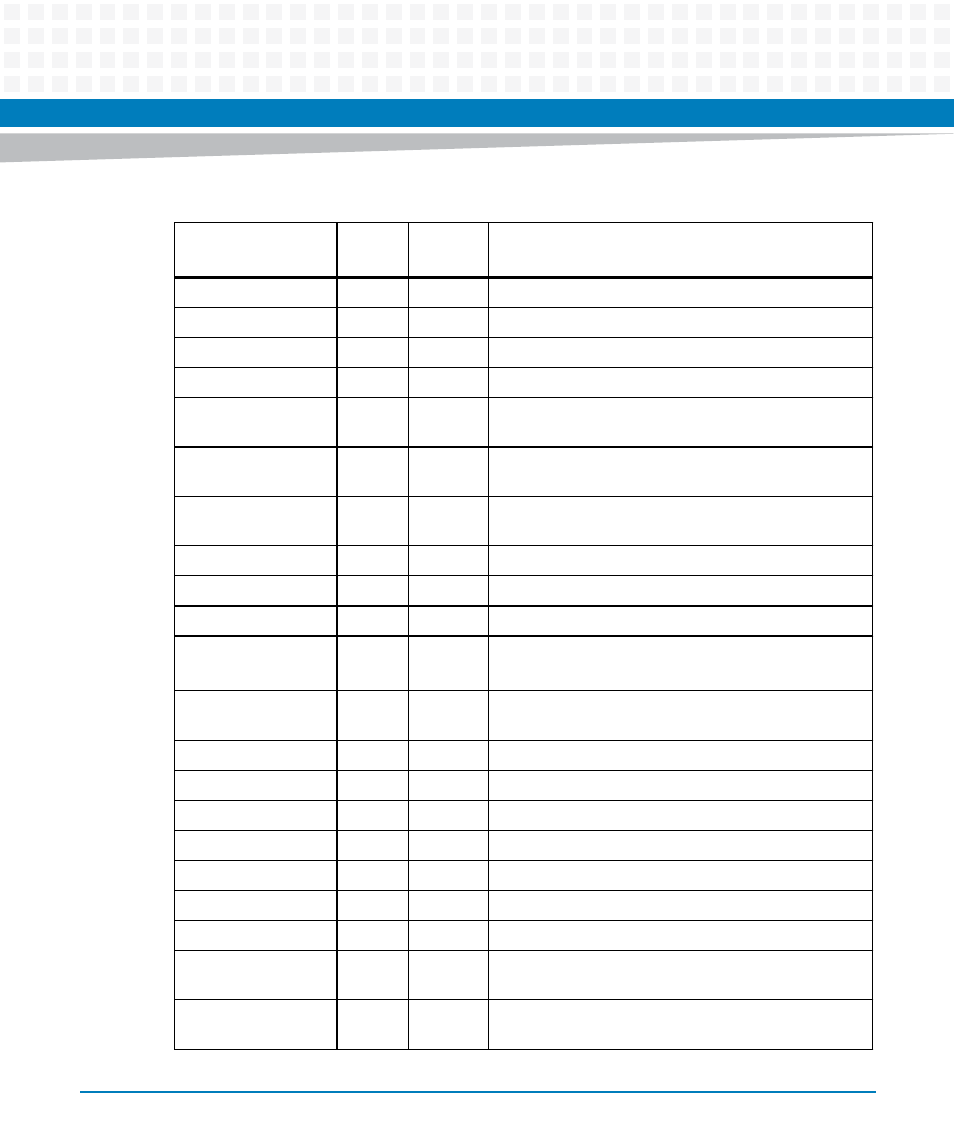

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

127

0x21

r/w1c

w

Internal Interrupt Status Register (See,

0x22

r

-

Telecom Interrupt Status Register (See,

)

0x23

r/w

-

Telecom Interrupt Control Register (See,

)

0x24

r

-

External Interrupt Status Register (See,

0x25-0x27

r/w

-

Interrupt Mask and Map Registers (See,

Interrupt Mask and Map Registers

0x30- 0x37

r/w

r/w

CPU0 Hot Plug I2C IO Expander Registers (See,

5, CPU0 Hot Plug I2C IO Expander Registers

0x38-0x3F

r/w

r/w

CPU1 Hot Plug I2C IO Expander Registers (See,

5, CPU0 Hot Plug I2C IO Expander Registers

0x40

r

r/w

Flash Status Register (See,

0x41

r/w

r

PCH Output Enable Register (See,

0x42

r/w

-

RTM SPI Address/Command Register (See,

0x43

r/w

-

RTM SPI Write Register (

)

RTM SPI Read Register (See,

)

0x48

r/w

r

Update Channel Equalization Control Register (See,

0x4A

r/w

r

RTM USB Control Register (See,

0x4B

-

r

RTM Status Register (See,

0x4C

-

r/w1c

RTM Interrupt Status Register (See,

)

0x50

r/w

r

LED Control Register (See,

)

0x52

r

r

Spare Signal Status Register (See,

)

0x54

r

r

CPU Presence Detection Register (See,

)

0x57

r

r

CPU Error Status Register (See,

)

0x60

r/w

-

Telecom Clock Monitor Control Register (See,

0x61

r/w1c

-

Telecom Clock Monitor Status Register (See,

Table 5-38 FPGA Register Map Overview (continued)

LPC Address Offset

LPC I/O

IPMC I2C

Description