Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 118

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

118

5.1.4.2.8 Line Status Register (LSR)

This register provides status information to the processor concerning the data transfers. Bits 5

and 6 show information about the transmitter section. The rest of the bits contain information

about the receiver.

In non-FIFO mode, three of the LSR register bits, parity error, framing error, and break

interrupt, show the error status of the character that has just been received. In FIFO mode,

these three bits of status are stored with each received character in the FIFO. LSR shows the

status bits of the character at the top of the FIFO. When the character at the top of the FIFO has

errors, the LSR error bits are set and are not cleared until software reads LSR, even if the

character in the FIFO is read and a new character is now at the top of the FIFO.

5

Autoflow control enable (AFE):

1: Autoflow control enabled (auto-RTS# and auto-CTS# or

auto-CTS# only enabled)

0: Autoflow control disabled

0

LPC: r/w

7:6

Reserved

0

LPC: r

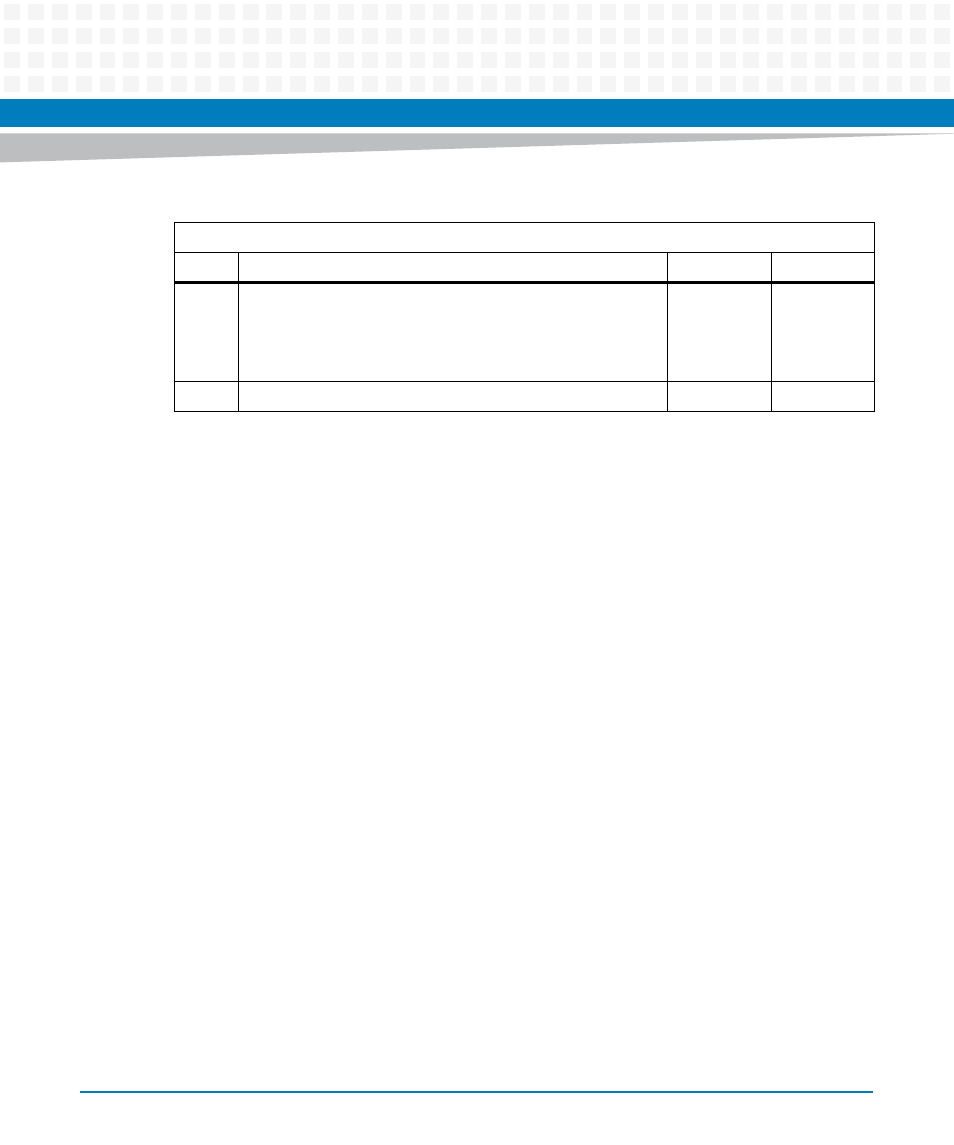

Table 5-32 Modem Control Register (MCR) (continued)

LPC IO Address: Base + 4

Bit Description

Default

Access