14 s-states control register, 15 nmi control status registers, Table 5-65 – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 149: S-states control register, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

149

5.1.14 S-States Control Register

IPMC can initiate S-State transitions:

S0 to S3. Triggered with SIC low pulse

S3, S4 or S5 to S0: Triggered with short PWRBTN low pulse

S0 to S5: Trigger graceful Shutdown with short PWRBTN low pulse

S0 to S5: Trigger forced Shutdown with long PWRBTN low pulse

5.1.15 NMI Control Status Registers

IPMC can initiate a NMI. Host can identify NMI comes from IPMC.

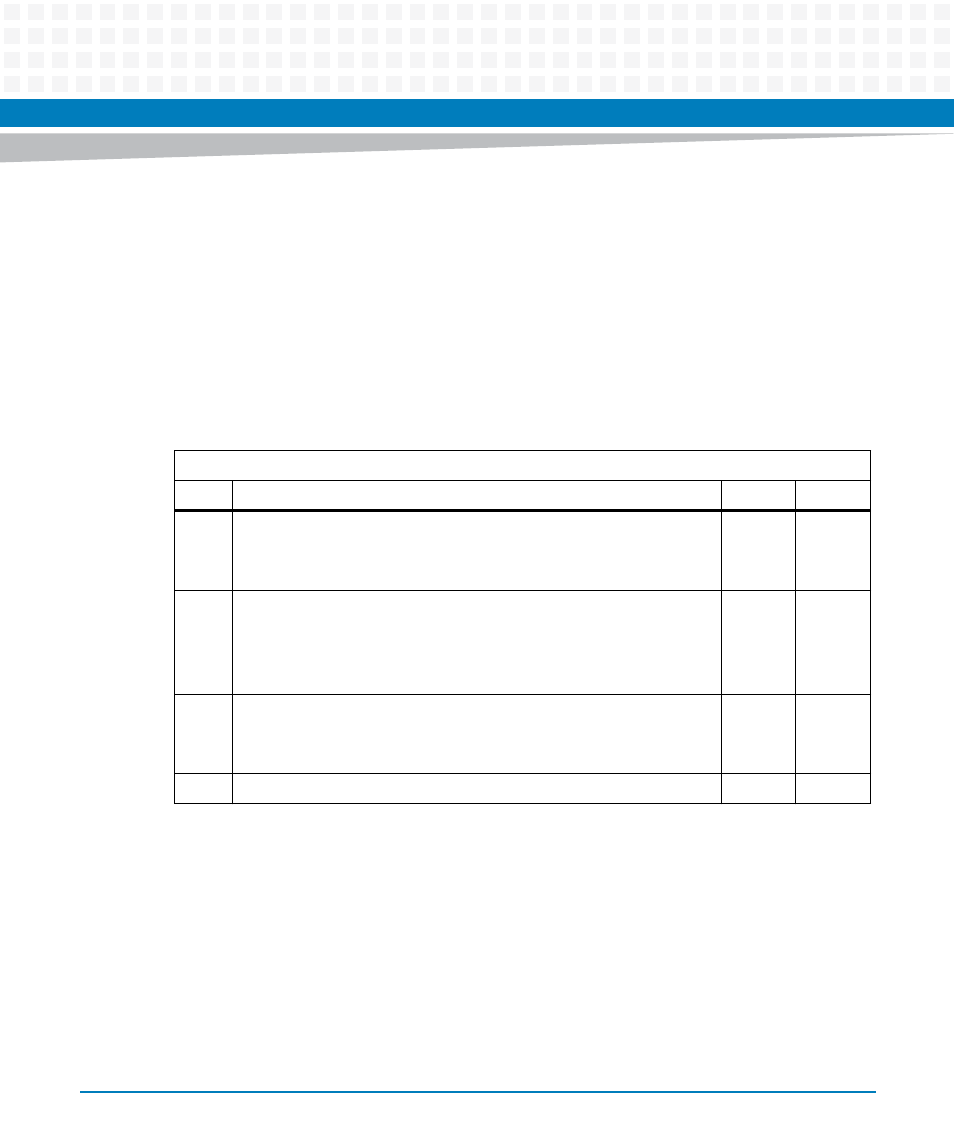

Table 5-65 S-States Control Register

Address Offset: 0x1F

Bit

Description

Default

Access

0

SCI pulse generation. Minimum low pulse width is 45ms:

0: No action

1: Generate SCI low pulse. Trigger S0 -> S3 transition

-

IPMC: w

1

PWRBTN pulse generation. Minimum low pulse width is 32ms:

0: No action

1: Generate PWRBTN low pulse. Trigger S3/S5 -> S0 transition

or when in S0 a “graceful” shutdown is triggered.

-

IPMC: w

2

Power Button Override Function. PWRBTN low pulse is 5s.

0: No action

1: Generate PWRBTN long low pulse. Forced transition to S5

-

IPMC: w

7:3

Reserved -

-