Table 5-77, Flash status register, Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 158

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

158

The IPMC Target Boot Flash selection will become active with next platform reset. When the

bits, TARGET_BOOT_SELECT and CURRENT_BOOT_SELECT are different, an alternate BIOS

needs to be selected. In this case the platform reset will be transformed by the FPGA logic to

payload power cycle including the ME. This is done to guarantee no SPI access to boot flash

when switching the other device.

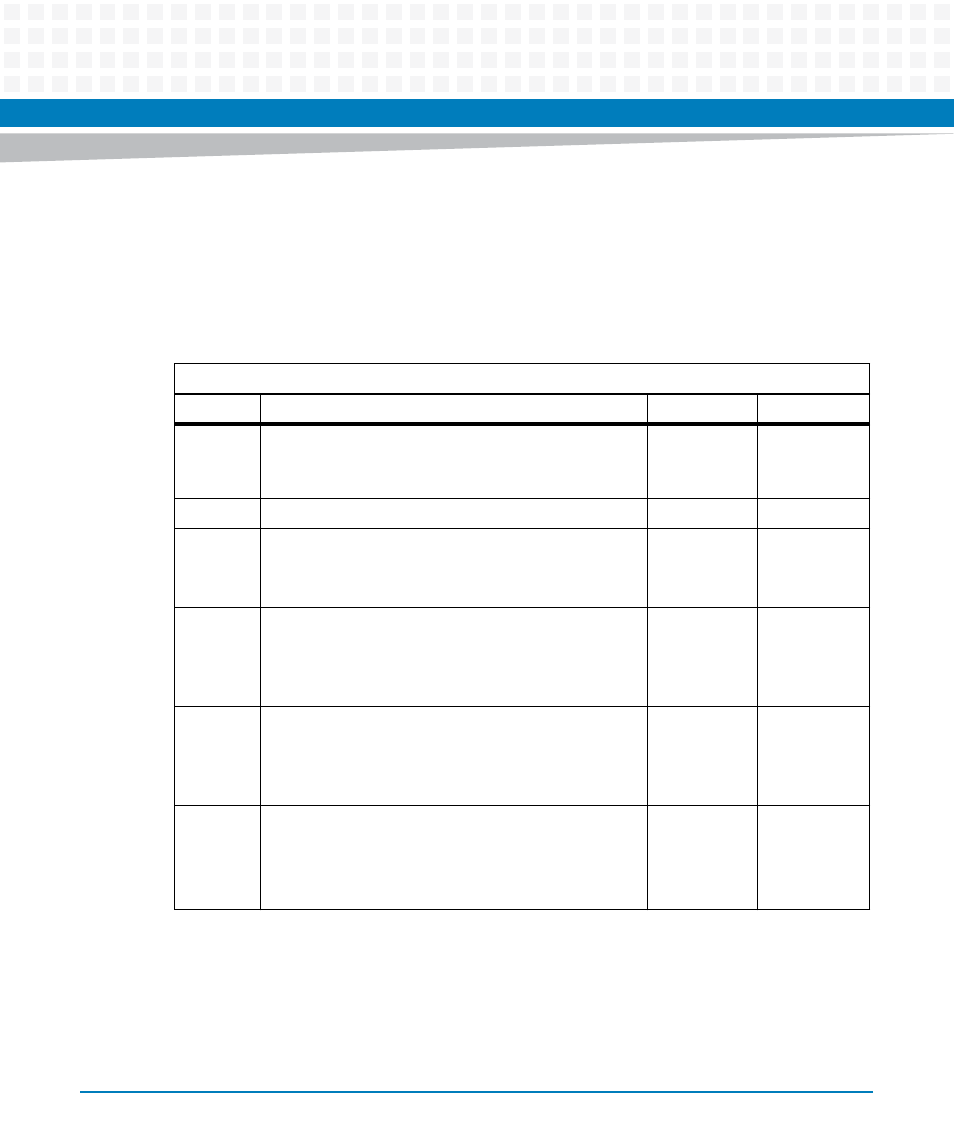

Table 5-77 Flash Status Register

Address Offset: 0x40

Bit

Description

Default

Access

0

CURRENT_BOOT_SELECT: Current Boot Flash

selection.

Is valid until next platform reset.

0

r

3:1

Reserved

0

r

4

TSOP or PLCC Boot select. Signal BOOT_TSOP.

0: TSOP selected

1: PLCC selected

Ext.

0: SW1.3 OFF

1: SW1.3 ON

r

5

Manual Boot Flash select enable. Signal

BOOT_SEL_EN_.

0: Signal BOOT_SELECT selects active boot flash

1: Switch SW3.2 selects the active Boot Flash.

Ext.

0: SW3.1 OFF

1: SW3.1 ON

r

6

Manual Boot Flash select. Signal BOOT_DEFAULT. Used

when SW3.1 is ON:

0: Selects Default Boot SPI Flash.

1: Selects Recover Boot SPI Flash.

Ext.

0: SW3.2 OFF

1: SW3.2 ON

r

7

TARGET_BOOT_SELECT. Target Boot Flash Selection.

0: Selects Default Boot SPI Flash

1: Selects Recovery Boot SPI Flash

Note: New flash selection valid with next platform reset

PWR_GOOD:

0

LPC: r

IPMC: r/w