2 i2c register decoding, 2 post code register, Table 5-4 – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 101: Ipmc spi register, Table 5-5, Post code register, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

101

5.1.1.1.3 LPC Firmware Decoding

The LPC interface never responds to LPC firmware accesses.

5.1.1.2

I2C Register Decoding

All I2C accesses from the IPMC towards the FPGA when the I2C master uses the I2C slave

address 0x7F (the corresponding 8bit slave address is 0xFE).

5.1.2

POST Code Register

The FPGA provides an 8 bit wide register to store POST codes to the LPC I/O address 0x80. The

two nibbles of the register are converted to 7 segment codes and are displayed as two hex

values by two 7 segment LED Displays.

The IPMC can read the POST code using the SPI interface (with the signal IPMC_SPI_SS_FPGA_

asserted) and the SPI address 0x7F.

The two 7 segment LED displays are also used for power failure indication.

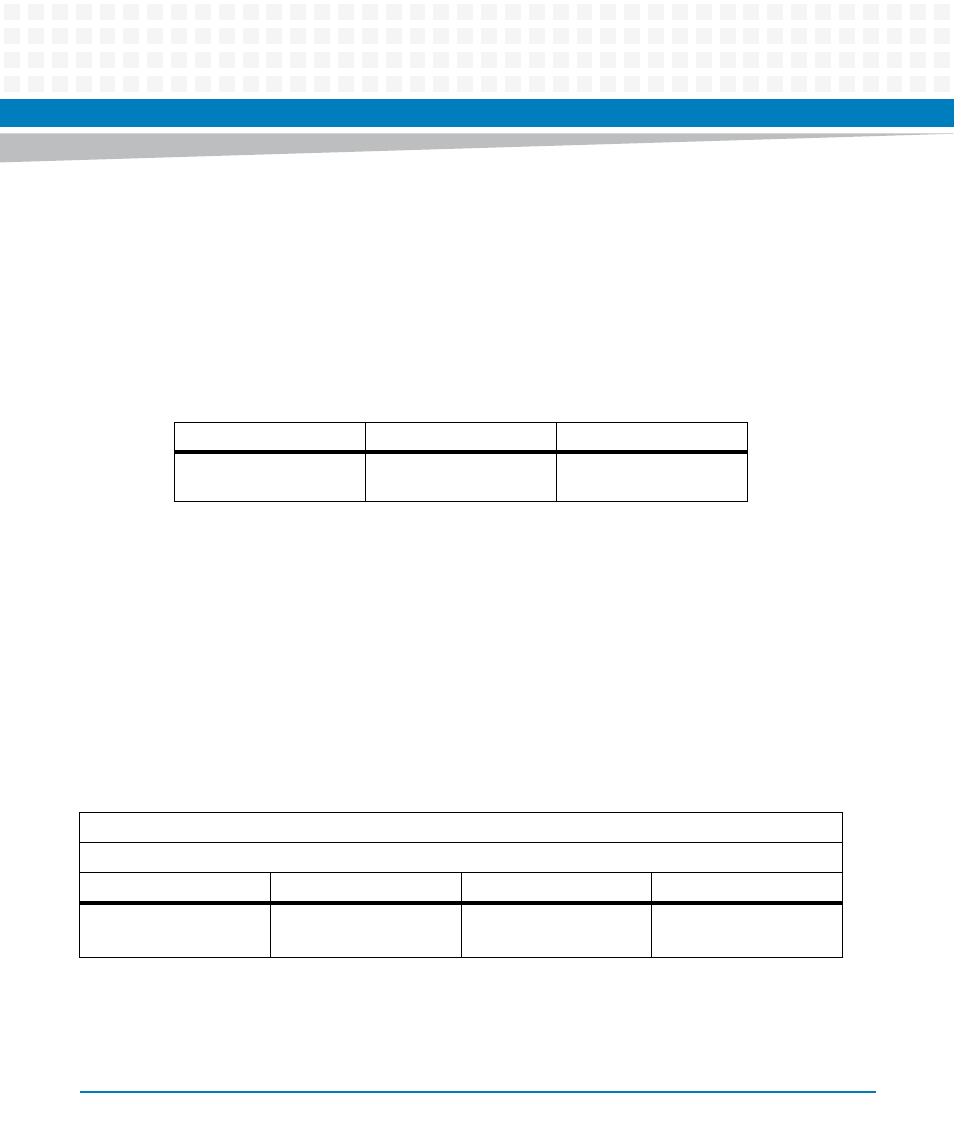

Table 5-4 IPMC SPI Register

I2C Address Range

Address Range Name

Description

0x00 - 0x7F

IPMC_REGISTERS

All FPGA Registers which

are accessible from IPMC

Table 5-5 POST Code Register

LPC I/O Address: 0x80

IPMC I2C Address: 0x7f

Bit

Description

Default

Access

7:0

POST codes from host

0

LPC: r/w

IPMC: r