5 fpga register mapping, 1 lpc i/o register map, 2 ipmc i2c register map – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 125: Table 5-38, Fpga register map overview, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

125

5.1.5

FPGA Register Mapping

5.1.5.1

LPC I/O Register Map

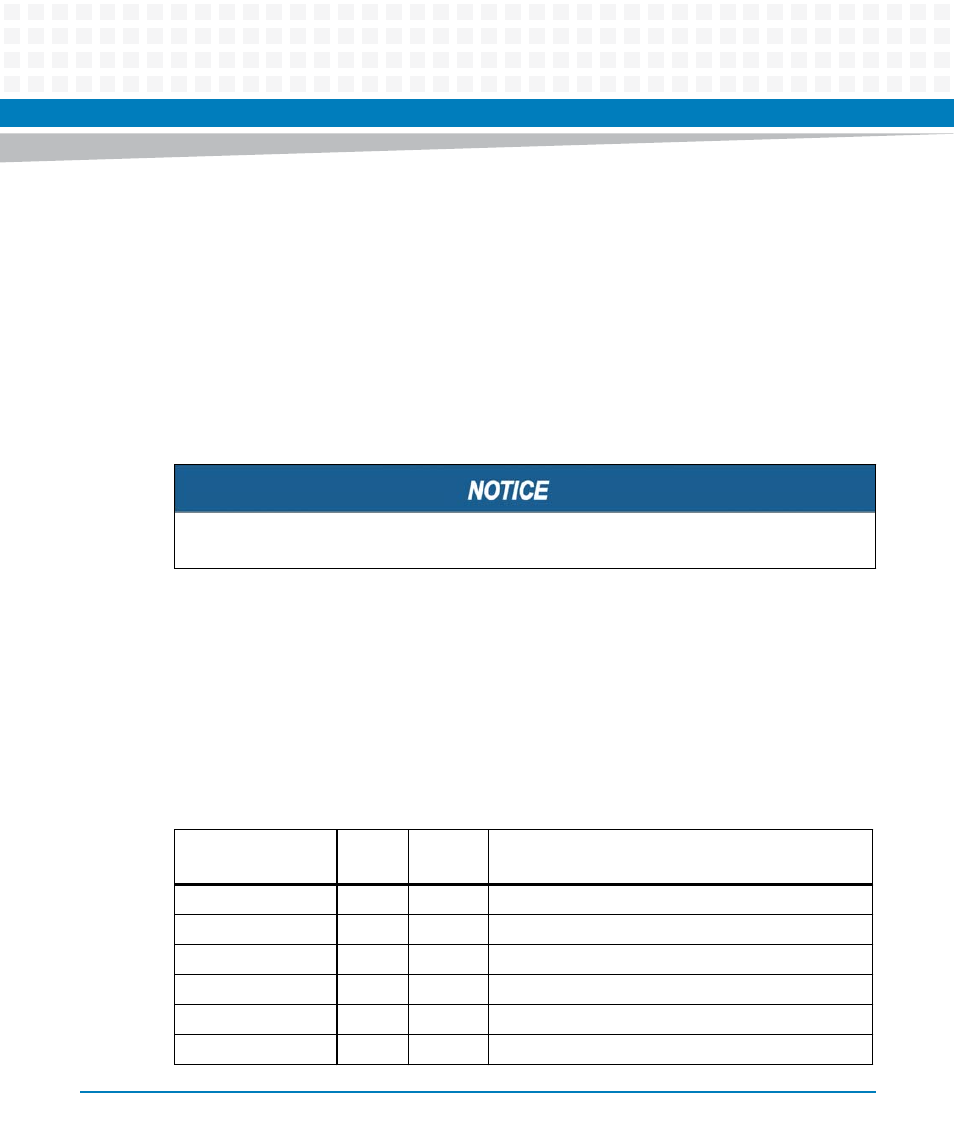

The FPGA registers can be accessed via LPC I/O cycles in the I/O address range REGISTERS. See

FPGA Register Map Overview. For a LPC register access the host uses the base

address, 0x600. Individual registers can be accessed by adding an offset to the base address.

An LPC I/O write access to an address not listed in this table or marked with an “-” in the LPC I/O

column is ignored. A corresponding read access delivers always zero – used and reserved for

future extensions. A reserved register is read only and deliver always zero. A reserved bit is read-

only and always reads zero.

5.1.5.2

IPMC I2C Register Map

Some FPGA registers may be accessed via IPMC Private I2C transactions (Slave address 0x7F).

See

FPGA Register Map Overview. An IPMC write access to an address not listed in

this table or marked with an “-” in the IPMC I2C column is ignored. A corresponding read access

delivers always zero. The address offsets not mentioned below are not used and reserved for

future extensions. A reserved register is read-only and always deliver zero. A reserved bit is

read-only and always reads zero.

LPC I/O Address = 0x600 + Address Offset

Table 5-38 FPGA Register Map Overview

LPC Address Offset

LPC I/O

IPMC I2C

Description

0x00-0x01

r

r

Module Identification Register (See,

0x02

r

r

FPGA Version Register (See,

)

0x03

r/w

r

Serial Redirection Control Register (See,

0x04

r

r/w

Serial over LAN Control Register (See,

)

0x05

r

r/w

Serial Line Routing Register (See,

)

0x06

r

r/w

IPMC Power Level Register