Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 128

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

128

1

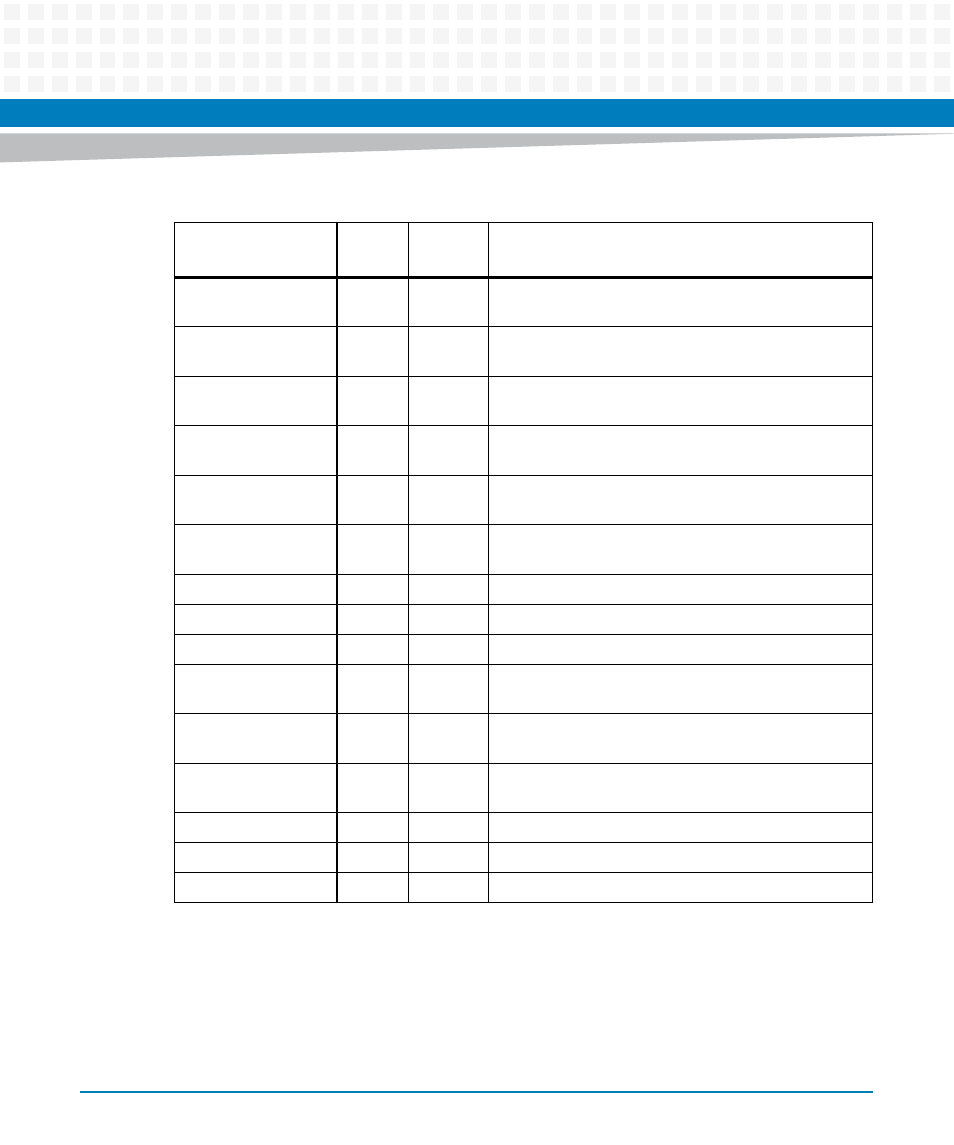

For LPC I/O address 0x80 is used. See

POST Code Register.

0x62

r/w1c

-

Telecom Clock Monitor Out of Range Register (See,

0x63

r/w

-

Telecom Clock Monitor Select Register (See,

0x64

r/w

-

Telecom Clock Monitor Time Base Register (See,

0x66-0x67

r/w

-

Telecom Clock Monitor Frequency/Period Register

(See,

0x68-0x69

r/w

-

Telecom Clock Monitor Lower Limit Register (See,

0x6A-0x6B

r/w

-

Telecom Clock Monitor Upper Limit Register (See,

0x74

r/w

r

BIOS Version Register 1 (See,

)

0x75

r/w

r

BIOS Version Register 2 (See,

)

0x76

r/w

r

BIOS Version Register 3 (See,

)

0x78

r

r/w

IPMC BIOS Communication Register 1 (See,

0x79

r

r/w

IPMC BIOS Communication Register 2 (See,

0x7A

r

r/w

IPMC BIOS Communication Register 3 (See,

0x7D

r/w

r

LPC Scratch Register (See,

0x7E

r

r/w

IPMC Scratch Register (See,

)

0x7F

1

r/w

r

POST Code Register (See,

)

Table 5-38 FPGA Register Map Overview (continued)

LPC Address Offset

LPC I/O

IPMC I2C

Description