Receive data path description, Scc/escc user manual – Zilog Z80230 User Manual

Page 96

SCC/ESCC

User Manual

UM010903-0515

Data Communication Modes

89

nous modes, the SDLC flag character (7E hex) is programmed in WR7 and is loaded into the

Transmit Shift Register at the beginning and end of each message.

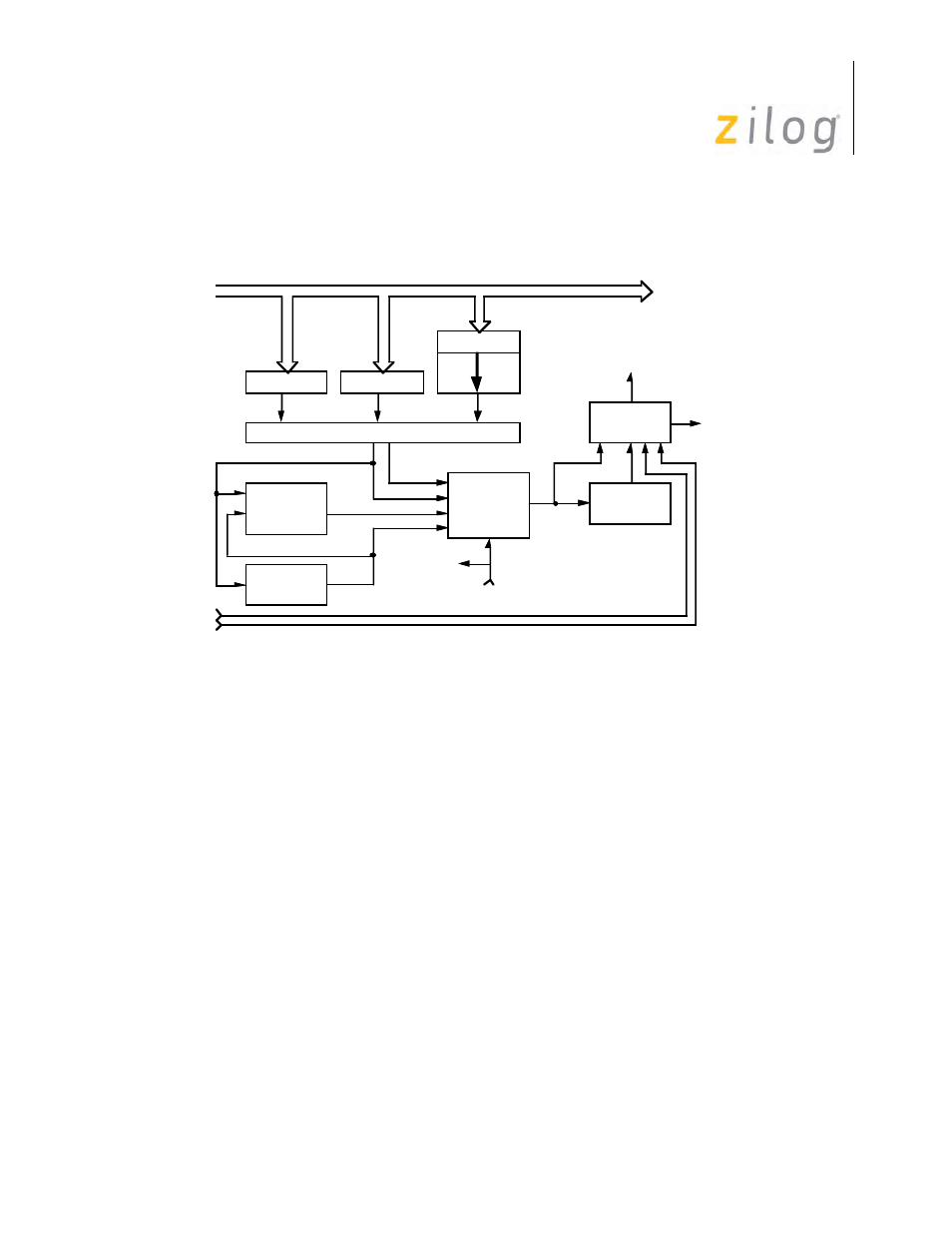

Transmit Data Path

Transmit Data Path

For asynchronous data, the Transmit Shift register is formatted with start and stop bits along with

the data; optionally with parity information bit. The formatted character is shifted out to the trans-

mit multiplexer at the selected clock rate. WR6 & WR7 are not used in Asynchronous mode.

Synchronous data (except SDLC/HDLC) is shifted to the CRC generator as well as to the transmit

multiplexer. SDLC/HDLC data is shifted to the CRC Generator and out through the zero insertion

logic (which is disabled while the flags are being sent). A 0 is inserted in all address, control,

information, and frame check fields following five contiguous 1s in the data stream. The result of

the CRC generator for SDLC data is also routed through the zero insertion logic and then to the

transmit multiplexer.

Receive Data Path Description

On the ESCC, the receiver has an 8-byte deep, 8-bit wide Data FIFO, while the NMOS/CMOS

version receiver has a 3-byte deep, 8-bit wide data buffer. In both cases, the Data buffer is paired

with an 8-bit Error FIFO and an 8-bit Shift Register. The receive data path is displayed in

.

This arrangement creates a 8-character buffer, allowing time for the CPU to service an interrupt or

for the DMA to acquire the bus at the beginning of a block of high-speed data. It is not necessary

To Other Channel

TX Buffer (1-Byte; NMOS/CMOS)

TX FIFO (4 Byte; ESCC)

WR8

WR6

WR7

20-Bit TX Shift Register

Final TX

MUX

Zero

Insert

5-Bit Delay

CRC-Gen

NRZI

Encode

Transmit

MUX & 2-Bit

Delay

ASYNC

SYNC

SDLC

CRC-SDLC

Transmit Clock

Internal TxD

TxD

From Receiver

Internal Data Bus

SYNC

SYNC

Register

Register