Scc/escc user manual – Zilog Z80230 User Manual

Page 61

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

54

data written. On the ESCC, the CRC has priority over the data. That means after the reception of

the Underrun/EOM (End Of Message) interrupt, it accepts the data for the next packet without col-

lapsing the packet. On the ESCC, if data was written during the time period described above, the

TBE bit (bit D2 of RR0) will not be set even if the second TxIP is guaranteed to set when the flag/

sync pattern was loaded into the Transmit Shift Register, as mentioned above (

and

on page 53). Hence, on the ESCC, there is no need to wait for the second TxIP bit to

set before writing data for the next packet and reducing the overhead.

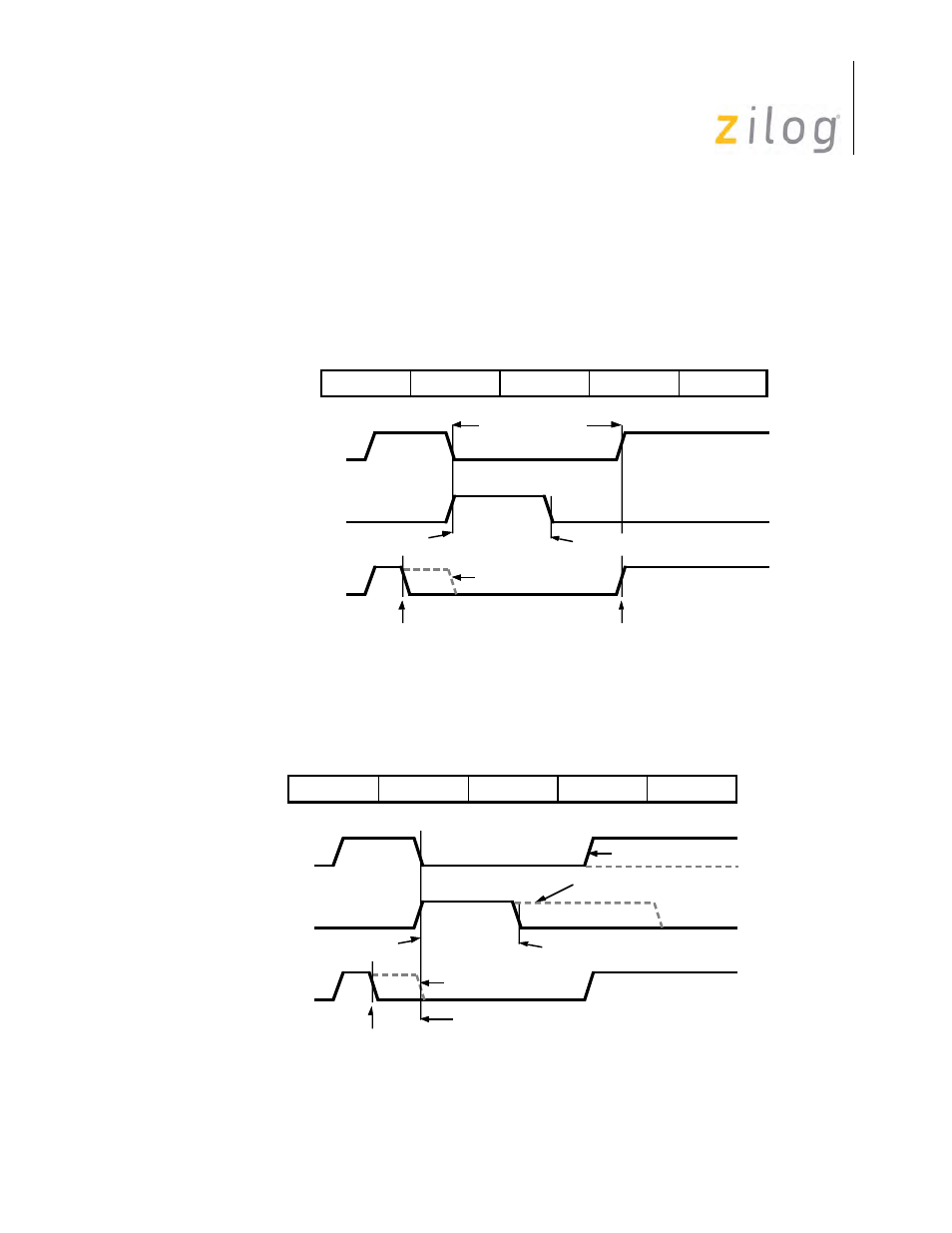

Operation of TBE, Tx Underrun/EOM and TxIP on NMOS/CMOS

Operation of TBE, Tx Underrun/EOM and TxIP on ESCC

TBE (RR0, D2)

Tx Underrun /EOM

Last Data -1

Last Data

CRC1

CRC2

Flag

TxIP

Can not write data

Indicating CRC get loaded

Reset Tx Underrun/EOM command

If TxIP Reset Command

NOT Issued

TxIP Reset Command

to Clear Interrupt

Indicating 1st byte of next packet

can be written this time

TBE

Tx Underrun /EOM

Last Data -1

Last Data

CRC1

CRC2

Flag

TxIP

Indicating CRC get loaded

Reset Tx Underrun/EOM Latch Command

If TxIP Reset Command

NOT Issued

TxIP Reset Command

to Clear Tx Interrupt

Data can be written to Tx FIFO after this point

When Auto EOM Reset has enabled

Set if Tx FIFO is Empty