Zilog Z80230 User Manual

Page 82

SCC/ESCC

User Manual

UM010903-0515

SCC/ESCC Ancillary Support Circuitry

75

synchronous. The data encoding selected is active even though the transmitter or receiver is idling

or disabled.

Data Encoding Methods

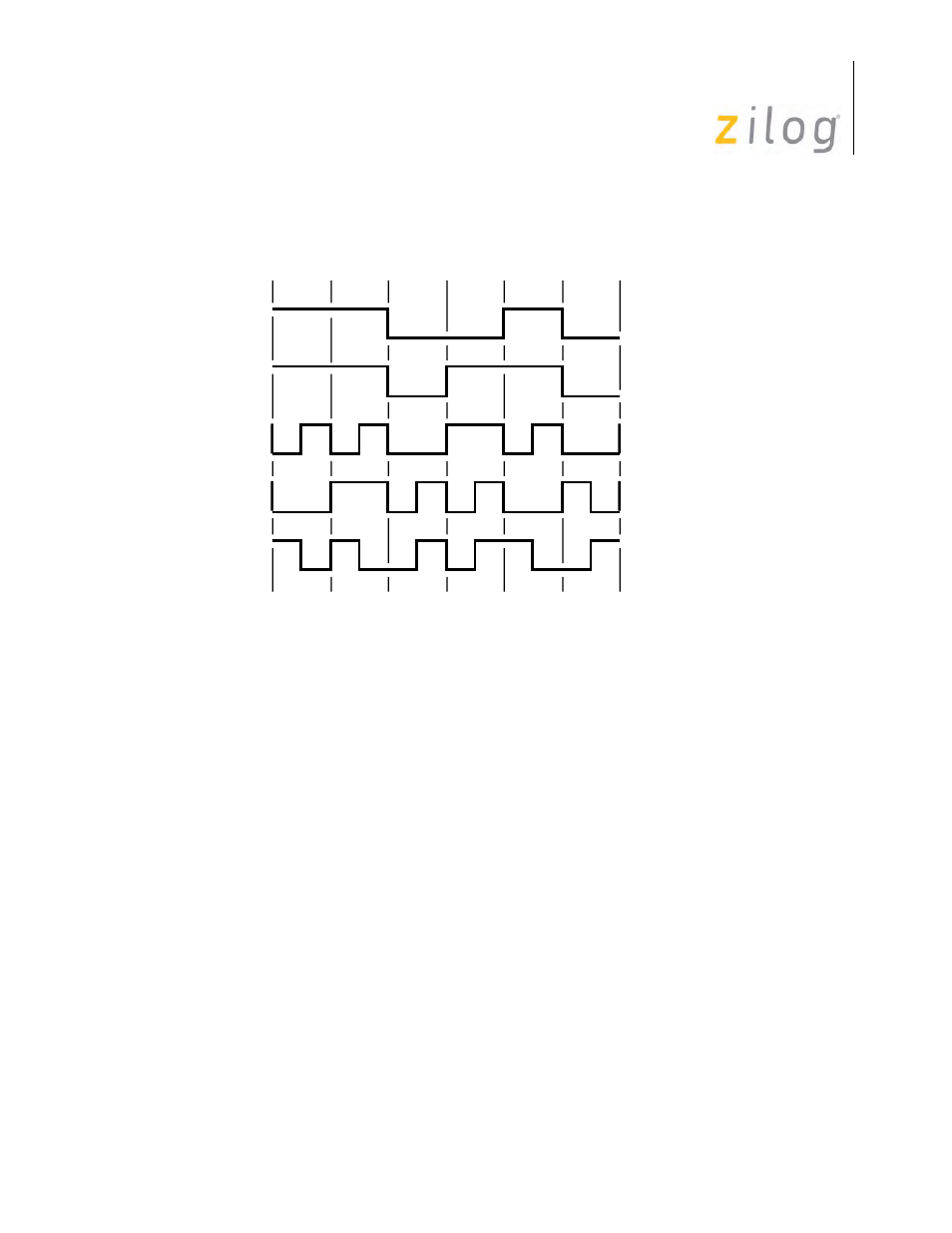

NRZ (Non-Return to Zero).

In NRZ, encoding a 1 is represented by a High level and a 0 is repre-

sented by a Low level. In this encoding method, only a minimal amount of clocking information is

available in the data stream in the form of transitions on bit-cell boundaries. In an arbitrary data

pattern, this may not be sufficient to generate a clock for the data from the data itself.

NRZI (Non-Return to Zero Inverted).

In NRZI, encoding a 1 is represented by no change in the

level and a 0 is represented by a change in the level. As in NRZ, only a minimal amount of clock-

ing information is available in the data stream, in the form of transitions on bit cell boundaries. In

an arbitrary data pattern this may not be sufficient to generate a clock for the data from the data

itself. In the case of SDLC, where the number of consecutive 1s in the data stream is limited, a

minimum number of transitions to generate a clock are guaranteed.

ESCC:

TxD Pin Forced High in SDLC feature. When the ESCC is programmed for SDLC mode with

NRZI data encoding and mark idle (WR10 D6=0, D5=1, D3=1), the TxD pin is automatically

forced high when the transmitter goes to the mark idle state. There are several different ways

for the transmitter to go into the idle state. In each of the following cases the TxD pin is forced

high when the mark idle condition is reached: data, CRC, flag and idle; data, flag and idle;

data, abort (on under-run) and idle; data, abort (command) and idle; idle flag and command to

idle mark. The Force High feature is disabled when the mark idle bit is reset. The TxD pin is

'$7$

15=

15=,

)0

%LSKDVH 0DUN

)0

%LSKDVH 6SDFH

0$1&+(67(5

%LW &HOO /HYHO

+LJK

/RZ

1R &KDQJH

&KDQJH

%LW &HQWHU 7UDQVLWLRQ

7UDQVLWLRQ

1R 7UDQVLWLRQ

1R 7UDQVLWLRQ

7UDQVLWLRQ

+LJK → /RZ

/RZ → +LJK