Figure – Zilog Z80230 User Manual

Page 60

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

53

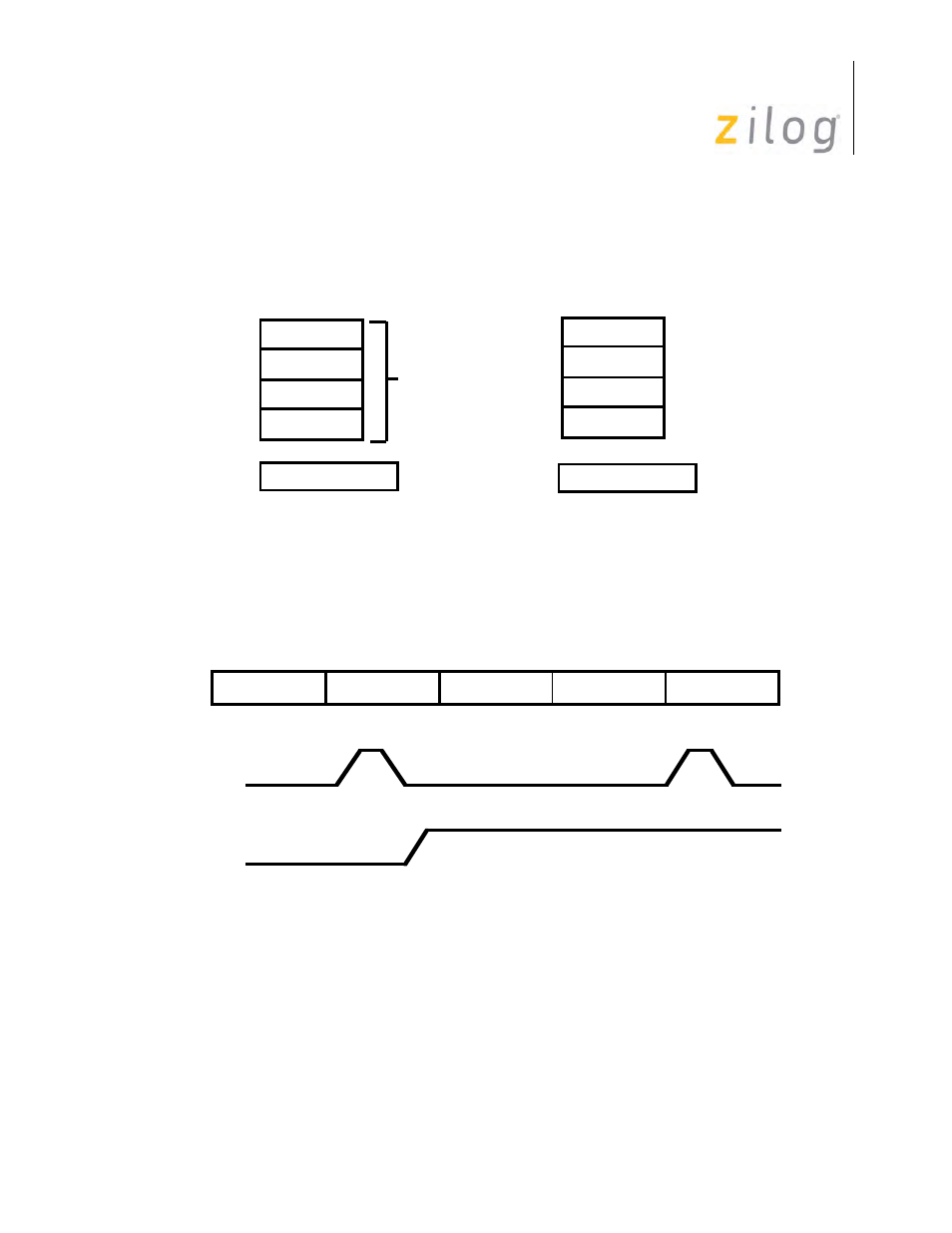

Transmit Buffer Empty Bit Status For ESCC For Both WR7' and WR7' D5=0

Transmit Interrupt Status When WR7' D5=0 For ESCC

TxIP Latching on the ESCC

Transmit Interrupt and Tx Underrun/EOM bit in Synchronous modes

As described in the section above, the behavior of the NMOS/CMOS version and the ESCC is

slightly different, particularly at the end of packet sending. On the NMOS/CMOS version, the data

has higher priority over CRC data; writing data before this interrupt would terminate the packet

illegally. In this case, the CRC byte(s) are replaced with a Flag or Sync pattern, followed by the

01

TxFIFO

Tx Shift Register

No Transmit Interrupt

TxIP = 0

04

03

02

04

03

02

Transmit Interrupt

TxIP = 1

Opening Flag

01

TXBE

TXIP Bit

Data

Data

CRC1

CRC2

Flag

TXIP 1

TXIP 2

Time "A"