Data encoding/decoding, Example in, Table – Zilog Z80230 User Manual

Page 81

SCC/ESCC

User Manual

UM010903-0515

SCC/ESCC Ancillary Support Circuitry

74

.

Other commonly used clock frequencies include 3.6846, 4.6080, 4.91520, 6.144, 7.3728, 9.216,

9.8304, 12.288, 14.7456, and 19.6608 (units in MHz).

Initializing the BRG is done in three steps. First, the time-constant is determined and loaded into

WR12 and WR13. Next, the processor must select the clock source for the BRG by setting bit D1

of WR14. Finally, the BRG is enabled by setting bit D0 of WR14 to 1.

The first write to WR14 is not necessary after a hardware reset if the clock source is the /

RTxC pin. This is because a hardware reset automatically selects the /RTxC pin as the BRG

clock source.

Data Encoding/Decoding

Data encoding is utilized to allow the transmission of clock and data information over the same

medium. This saves the need to transmit clock and data over separate medium as would normally

be required for synchronous data. The SCC provides four different data encoding methods,

selected by bits D6 and D5 in WR10. An example of these four encoding methods is displayed in

on page 75. Any encoding method is used in any X1 mode in the SCC, asynchronous or

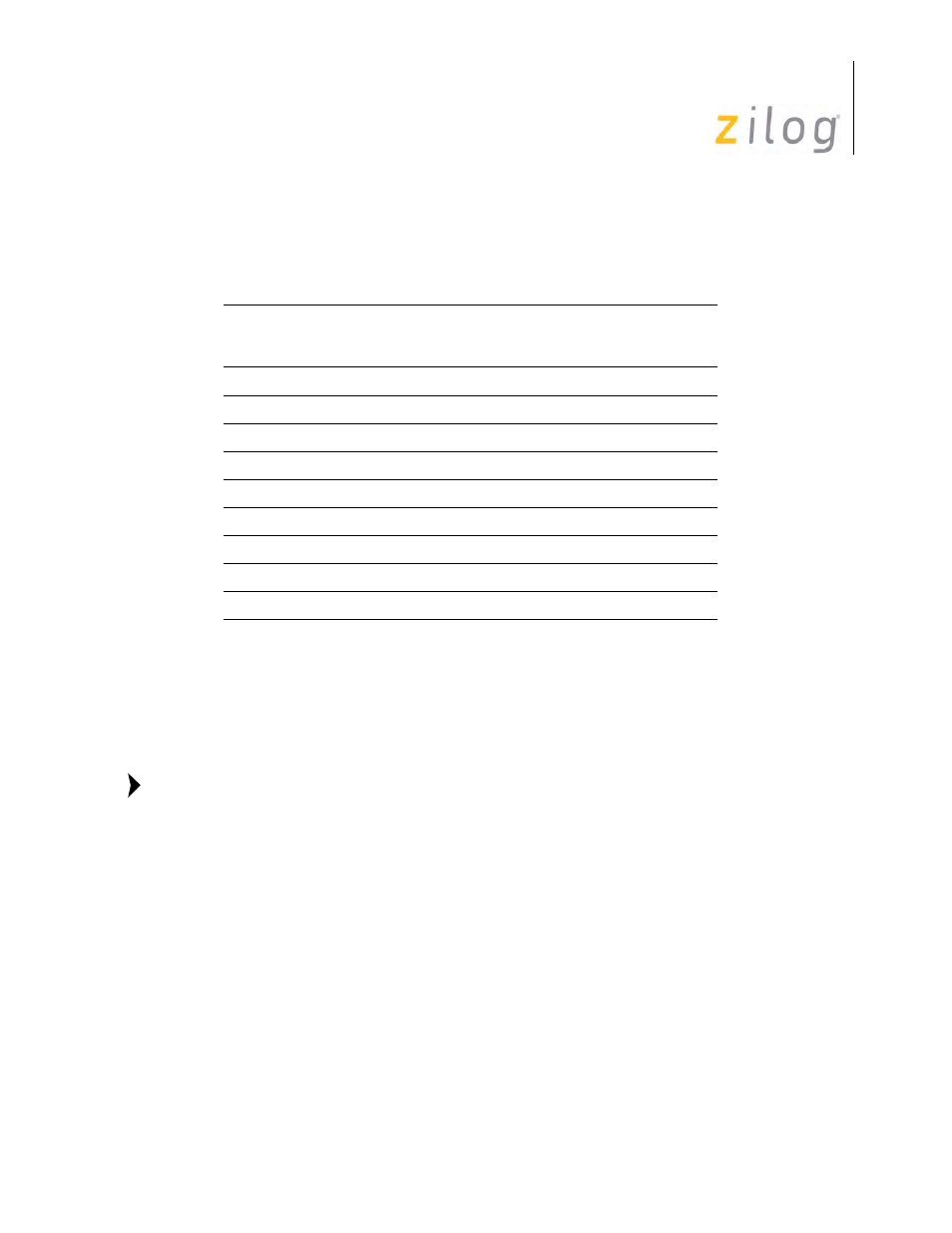

Baud Rates for 2.4576 MHz Clock and 16x Clock Factor

Baud Rate

Time Constant

Decimal

Hex

38400

0

0000

19200

2

0002

9600

6

0006

4800

14

000E

2400

30

001E

1200

62

003E

600

126

007E

300

254

00FE

150

510

01FE

TC

2.4576 10

6

2 16

150

----------------------------------- 2

–

510

=

=

Note: