Zilog Z80230 User Manual

Page 73

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

66

DMA Request On Transmit (using /DTR//REQ)

A second Request on Transmit function is available on the /DTR//REQ pin. This mode is selected

by setting D2 of WR14 to 1. /REQ goes Low when the Transmit FIFO is empty if WR7' D5=1, or

when the exit location of the Transmit FIFO is empty if WR7' D5=0. In the Request mode, /REQ

follows the state of the Transmit FIFO even though the transmitter is disabled. While D2 of WR14

is set to 0, the /DTR//REQ pin is /DTR and follows the inverted state of D7 in WR5. This pin is

High after a channel or hardware reset and in the DTR mode.

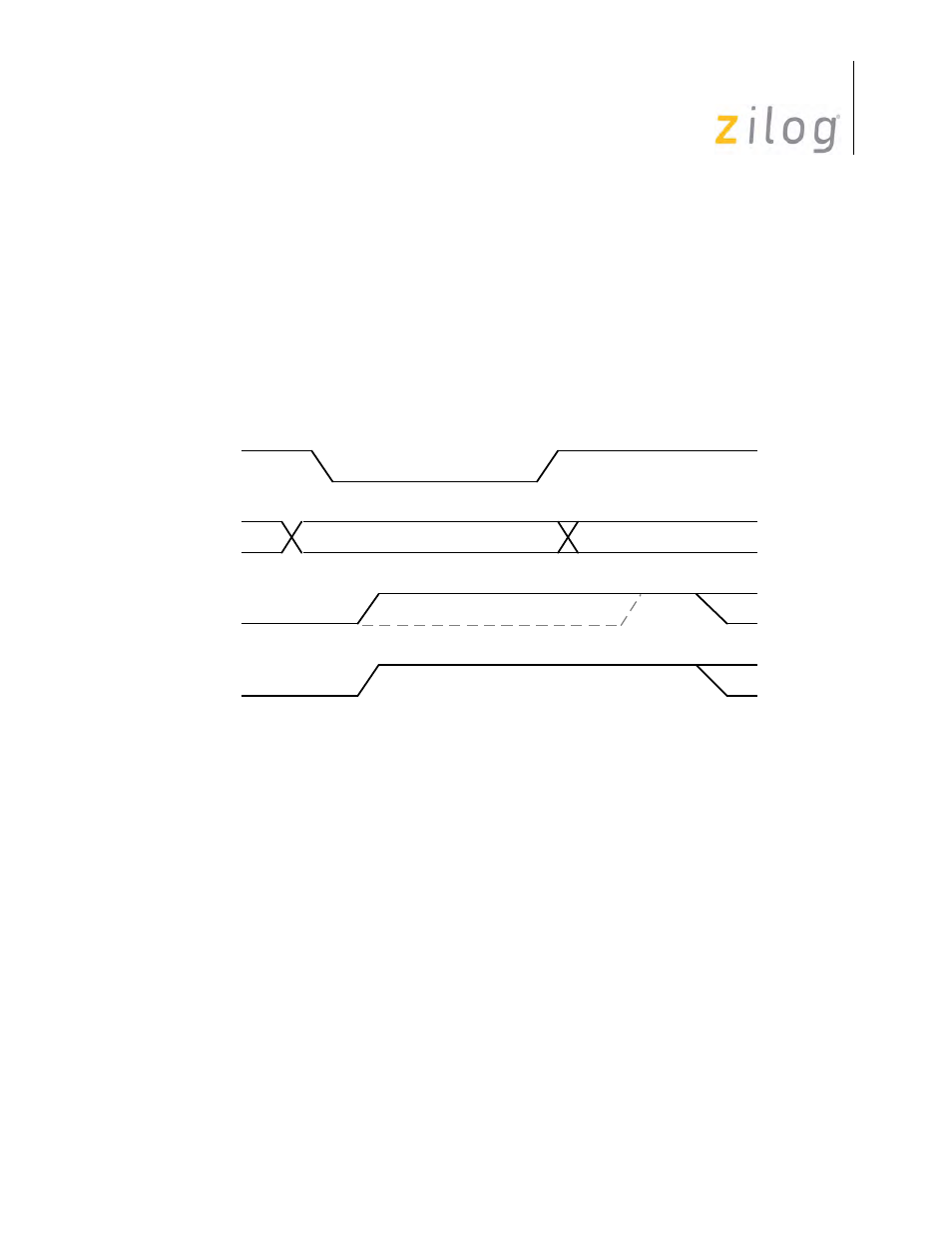

The /DTR//REQ pin goes inactive High between each transfer for a minimum of one PCLK cycle

(

/DTR//REQ Deassertion Timing

ESCC:

The timing of deactivation of this pin is programmable through WR7' bit D4. The /DTR//REQ

waits until the write operation has been completed before going inactive. Refer to Z85230/L AC

spec #35a TdWRr(REQ) and Z80230 AC spec #27a TdDSr(REQ). This mode is compatible with

the SCC and guarantees that any subsequent access to the ESCC does not violate the valid

access recovery time requirement.

If WR7' D4=1, the /DTR//REQ is deactivated with identical timing as the /W/REQ pin. Refer to

Z85230/L AC spec #35b TdWRr(REQ) and Z80230 AC spec #27b TdDSr(REQ). This feature is

beneficial to applications needing the DMA request to be deasserted quickly. It prevents a full

Transmit FIFO from being overwritten due to the assertion of REQUEST being too long and

being recognized as a request for more data.

/DTR//REQ

/WAIT//REQ

/DS or /WR

D7-D0

Transmit Data

ESCC WR7' D4 =1

ESCC WR7' D4 =0, or CMOS/NMOS version