Zilog Z80230 User Manual

Page 69

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

62

Wait On Receive

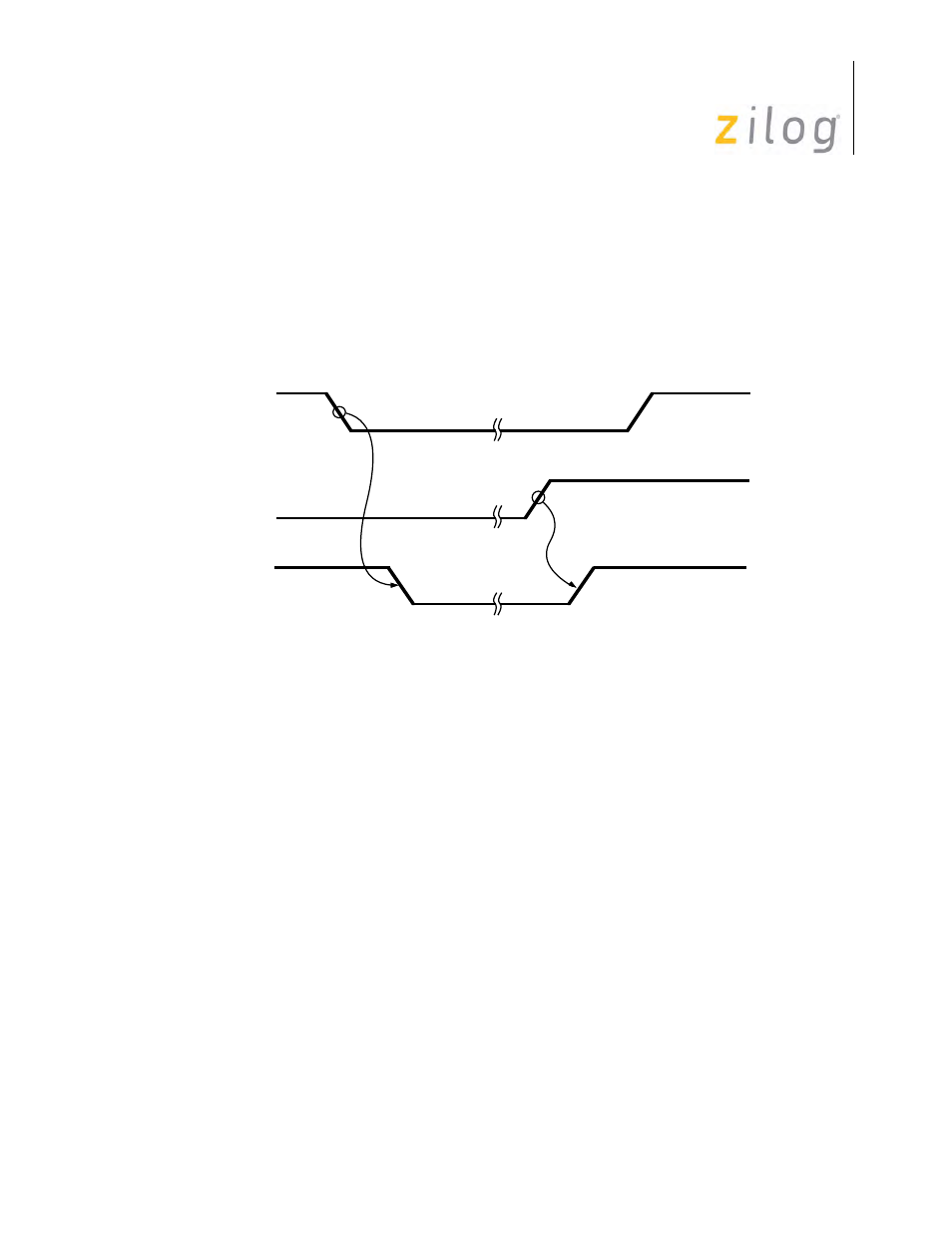

The Wait On Receive function is selected by setting D6 or WR1 to 0, D5 of WR1 to 1, and then

enabling the function by setting D7 of WR1 to 1. In this mode, the /W//REQ pin carries the /WAIT

signal, and is open-drain when inactive and Low when active. When the processor attempts to read

data from the Receive FIFO when it is empty, the SCC asserts /WAIT until a character has reached

the exit location of the FIFO (

).

Wait on Receive Timing

This allows the use of a block move instruction to transfer the receive data. In the case of the

Z80X30, /WAIT goes active in response to /DS going active, but only if RR8 is being accessed

and a read is attempted. In all other cases, /WAIT remains open-drain. In the case of the Z85X30, /

WAIT goes active in response to /RD going active, but only if the receive data FIFO is being

accessed, either directly or via the pointers. The /WAIT pin is released in response to the falling

edge of PCLK. Details of the timing are displayed in

/DS or /RD

(from Rx FIFO)

Rx Character

Available

/W//REQ

(=WAIT)

Character Available

FIFO Empty