Zilog Z80230 User Manual

Page 27

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

20

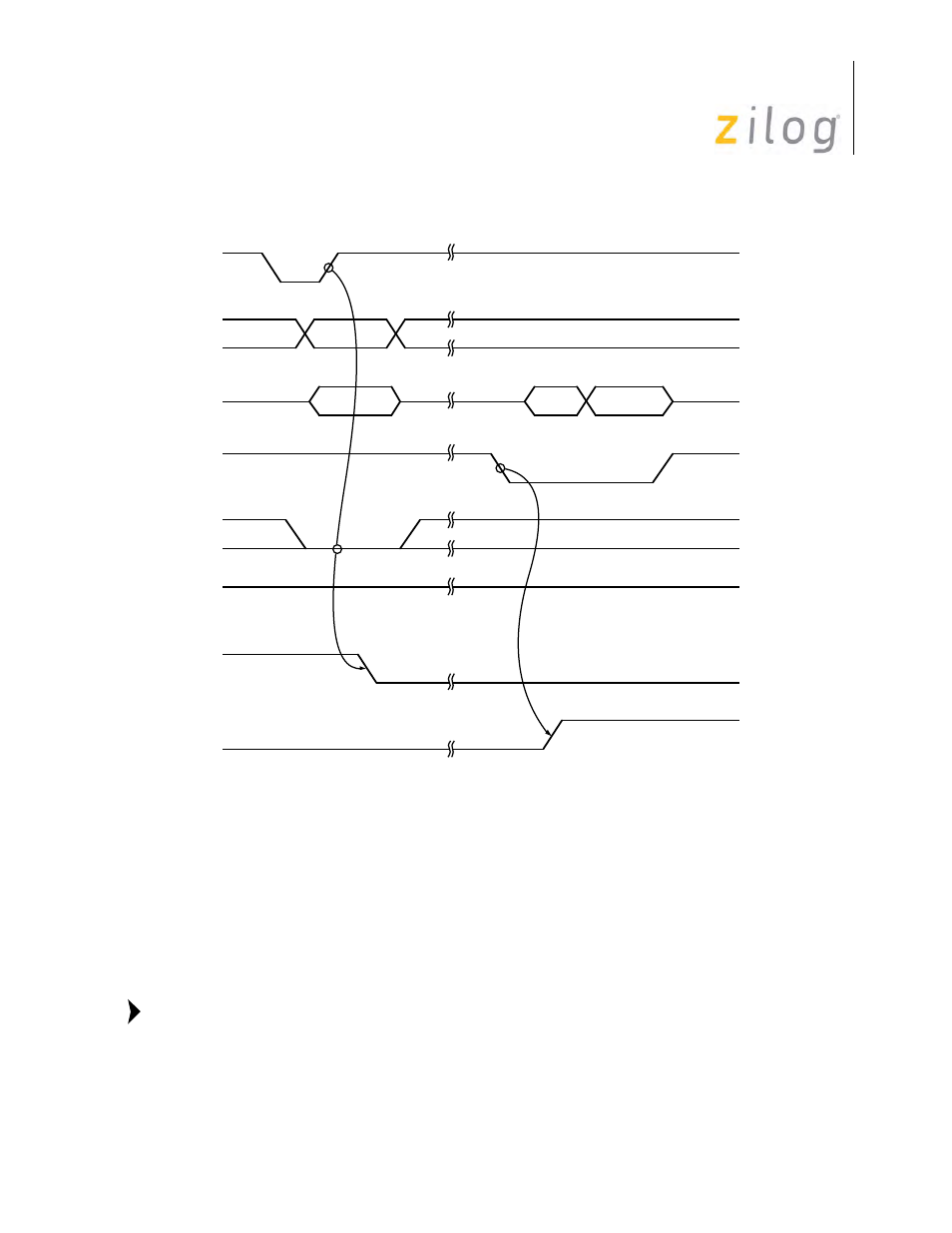

Z80X30 Interrupt Acknowledge Cycle

The Z80X30 samples the state of /INTACK on the rising edge of /AS, and AC parameters #7 and

#8 specify the setup and hold-time requirements. Between the rising edge of /AS and the falling

edge of /DS, the internal and external daisy chains settle (AC parameter #29). A system with no

external daisy chain should provide the time specified in spec #29 to settle the interrupt daisy-

chain priority internal to the SCC. Systems using an external daisy chain should refer to Note 5

referenced in the Z80X30 Read/Write & Interrupt Acknowledge Timing for the time required to

settle the daisy chain.

/INTACK is sampled on the rising edge of /AS. If it does not meet the setup time to the

first rising edge of /AS of the interrupt acknowledge cycle, it is latched on the next ris-

ing edge of /AS. Therefore, if /INTACK is asynchronous to /AS, it may be necessary to

add a PCLK cycle to the calculation for /INTACK to /RD delay time.

/AS

/CS0

/DS

/INTACK

IEI

IEO

Vector

/INT

AD7 - AD0

Note: