Zilog Z80230 User Manual

Page 62

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

55

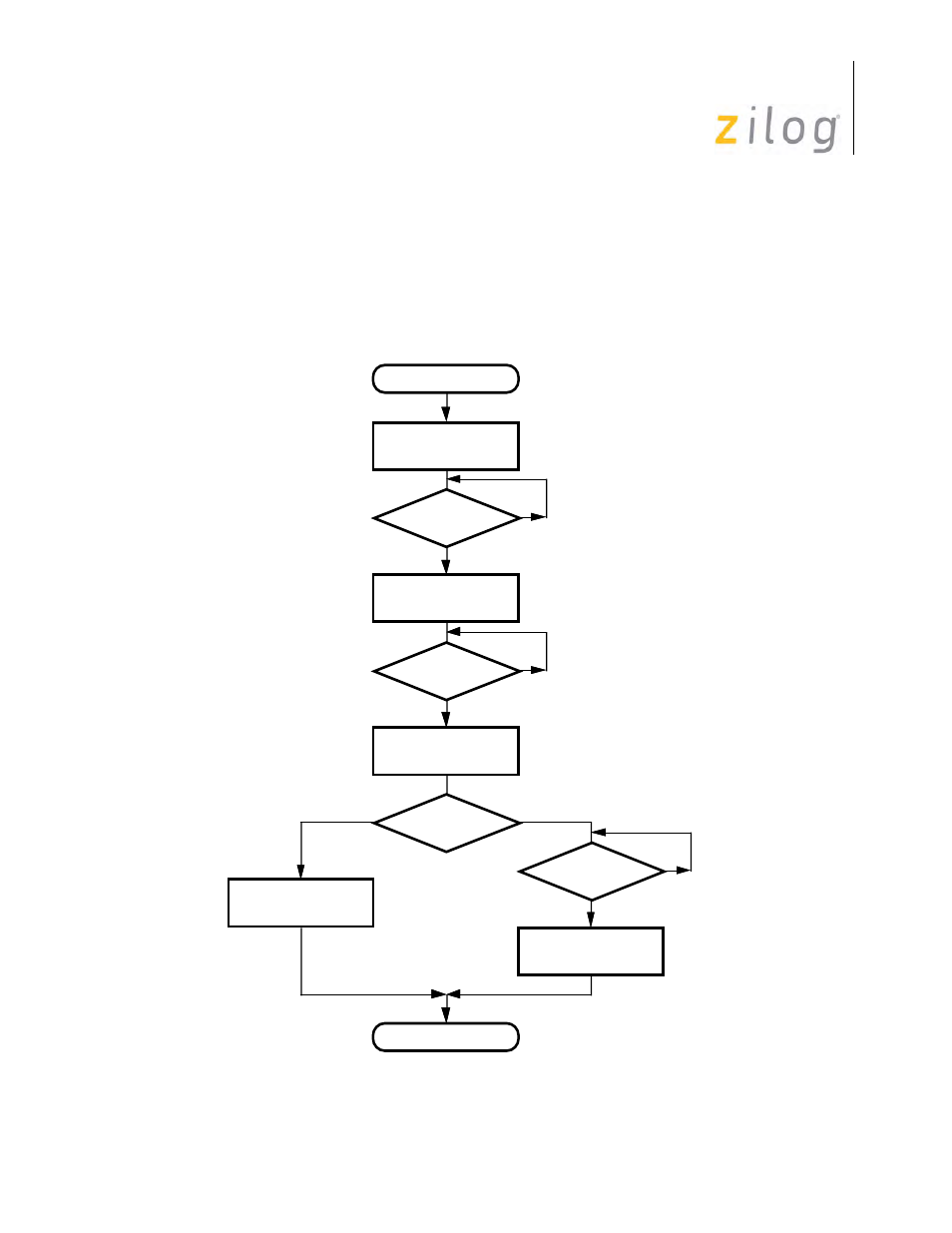

An example flowchart for processing an end of packet is displayed in

. The chart includes

the differences in processing between the ESCC and NMOS/CMOS version. In this chart, Tx IP

and Underrun/EOM INT can be processed by interrupts or by polling the registers. Note that this

flowchart does not have the procedures for interrupt handling, such as saving/restoring of registers

to be used in the ISR (Interrupt Service Routine), Reset IUS command, or return from interrupt

sequence.

Flowchart example of processing an end of packet

START

Write Last Data

TxIP=1 ?

(TBE=1)

Issue

Reset Tx IP command

Yes

No

Underrun/EOM

INT?

Issue Ext/Stat Int cmd

(to clear Ext/stat INT)

Yes

No

ESCC or

NMOS/CMOS

ESCC

NMOS/CMOS

Write 1st byte of

Next Packet (1 byte)

Yes

No

Write data for next

packet (max. 4 Bytes)

End

TxIP=1 ?

(TBE=1)