Zilog Z80230 User Manual

Page 220

SCC/ESCC

User Manual

UM010903-0515

Application Notes

213

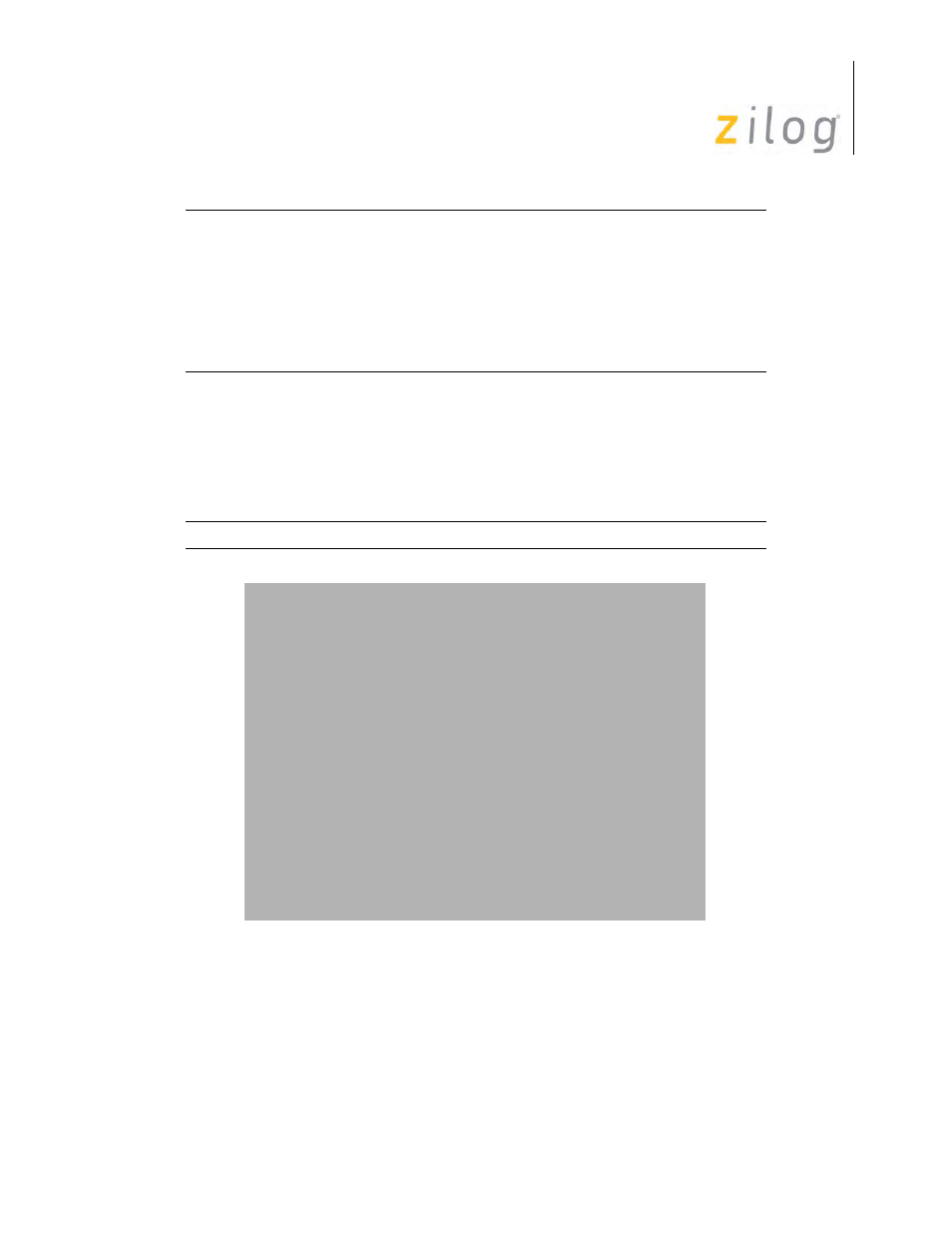

Z180 Memory Read Cycle Timing (One Wait State)

EPROM Interface

During an Opcode fetch cycle, data sampling of the bus is on the rising PHI clock edge of T3 and

on the falling edge of T3 during a memory read cycle. Opcode fetch cycle data sample timing is

half a clock cycle earlier. Table lists how a memory read cycles’ timing requirements are easier

than an opcode fetch cycle by half a PHI cycle time. If the timing requirements for an Opcode

15

tDRS

Data to Clock Setup

25

ns

16

tDRH

Data Read Hold Time

0

ns

22

tWRD1

Clock High to /WR Low

50

ns

23

tWDD

Clock Low to Write Data

Delay

60

ns

24

tWDS

Write Data Setup to /

WR Low

15

ns

25

tWRD2

Clock Low to /WR High

50

ns

26

tWRP

/WR Pulse Width

110

ns

27

tWDH

/WR High to Data Hold

Time

10

ns

Note: Parameter numbers in this table are in the Z180 technical manual.

No Symbol

Parameter

Min

Max

Units