Figure – Zilog Z80230 User Manual

Page 182

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

175

this register. This feature prevents missed status due to changes that take place when the read cycle

is in progress.

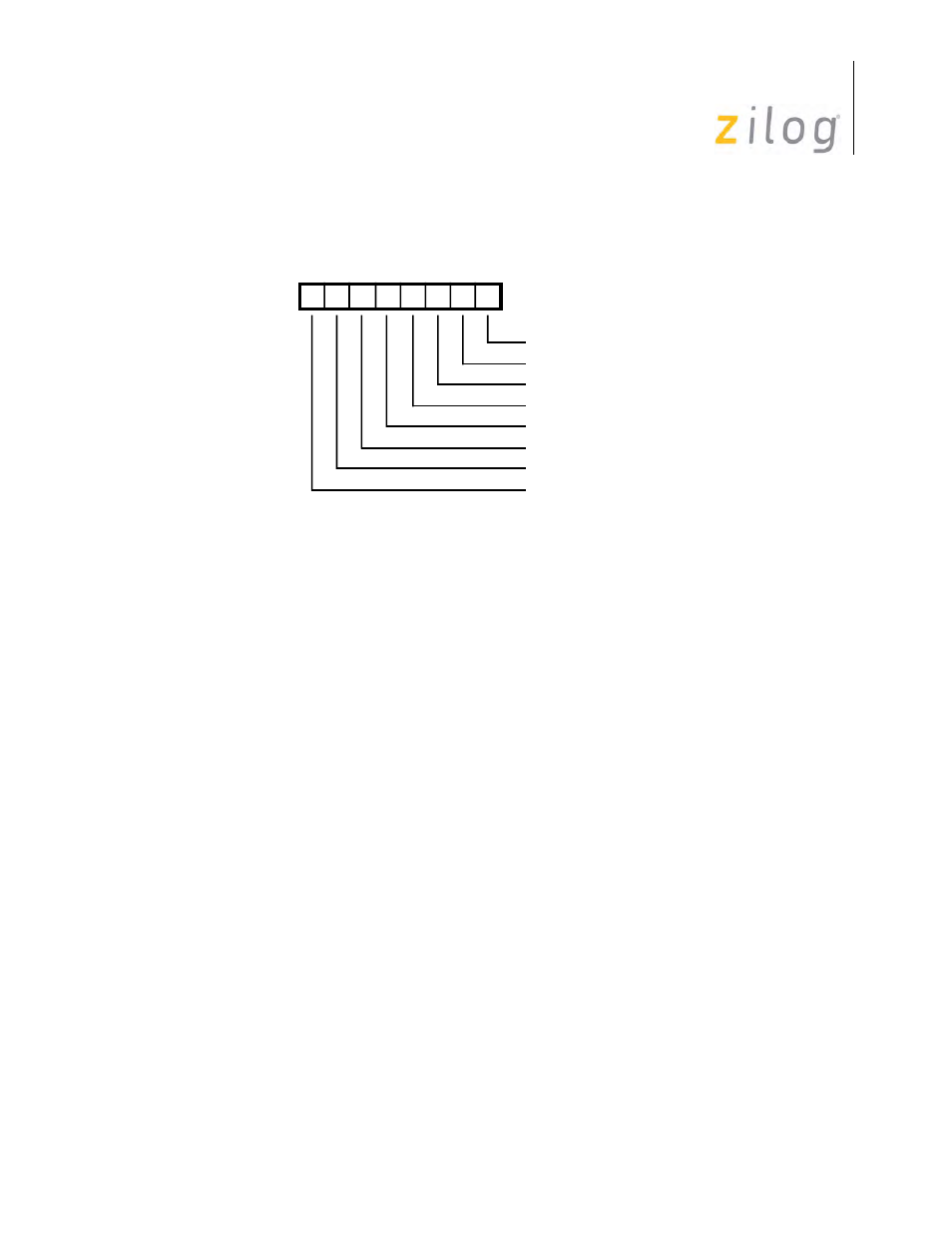

Read Register 0

Bit 7: Break/Abort status

In the Asynchronous mode, this bit is set when a Break sequence (null character plus framing

error) is detected in the receive data stream. This bit is reset when the sequence is terminated, leav-

ing a single null character in the Receive FIFO. This character is read and discarded. In SDLC

mode, this bit is set by the detection of an Abort sequence (seven or more 1s), then reset automati-

cally at the termination of the Abort sequence. In either case, if the Break/Abort IE bit is set, an

External/Status interrupt is initiated. Unlike the remainder of the External/Status bits, both transi-

tions are guaranteed to cause an External/Status interrupt, even if another External/Status interrupt

is pending at the time these transitions occur. This procedure is necessary because Abort or Break

conditions may not persist.

Bit 6: Transmit Underrun/EOM status

This bit is set by a channel or hardware reset when the transmitter is disabled or a Send Abort com-

mand is issued. This bit is only reset by the reset Tx Underrun/EOM Latch command in WR0.

When the Transmit Underrun occurs, this bit is set and causes an External/Status interrupt (if the

Tx Underrun/EOM IE bit is set).

Only the 0-to-1 transition of this bit causes an interrupt. This bit is always 1 in Asynchronous

mode, unless a reset Tx Underrun/EOM Latch command has been erroneously issued. In this case,

the Send Abort command can be used to set the bit to one and at the same time cause an External/

Status interrupt.

Bit 5: Clear to Send pin status

If the CTS IE bit in WR15 is set, this bit indicates the state of the /CTS pin while no interrupt is

pending, latches the state of the /CTS pin and generates an External/Status interrupt. Any odd

D7 D6 D5 D4 D3 D2 D1 D0

Read Register 0

Rx Character Available

Zero Count

Tx Buffer Empty

DCD

Sync/Hunt

CTS

Tx Underrun/EOM

Break/Abort