Dma requests, Figure – Zilog Z80230 User Manual

Page 70

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

63

Care must be taken when this mode is used. The /WAIT pin stays active as long as the Receive

FIFO remains empty. When the CPU access the SCC, the CPU remains in the wait state until data

gets into the Receive FIFO, freezing the system.

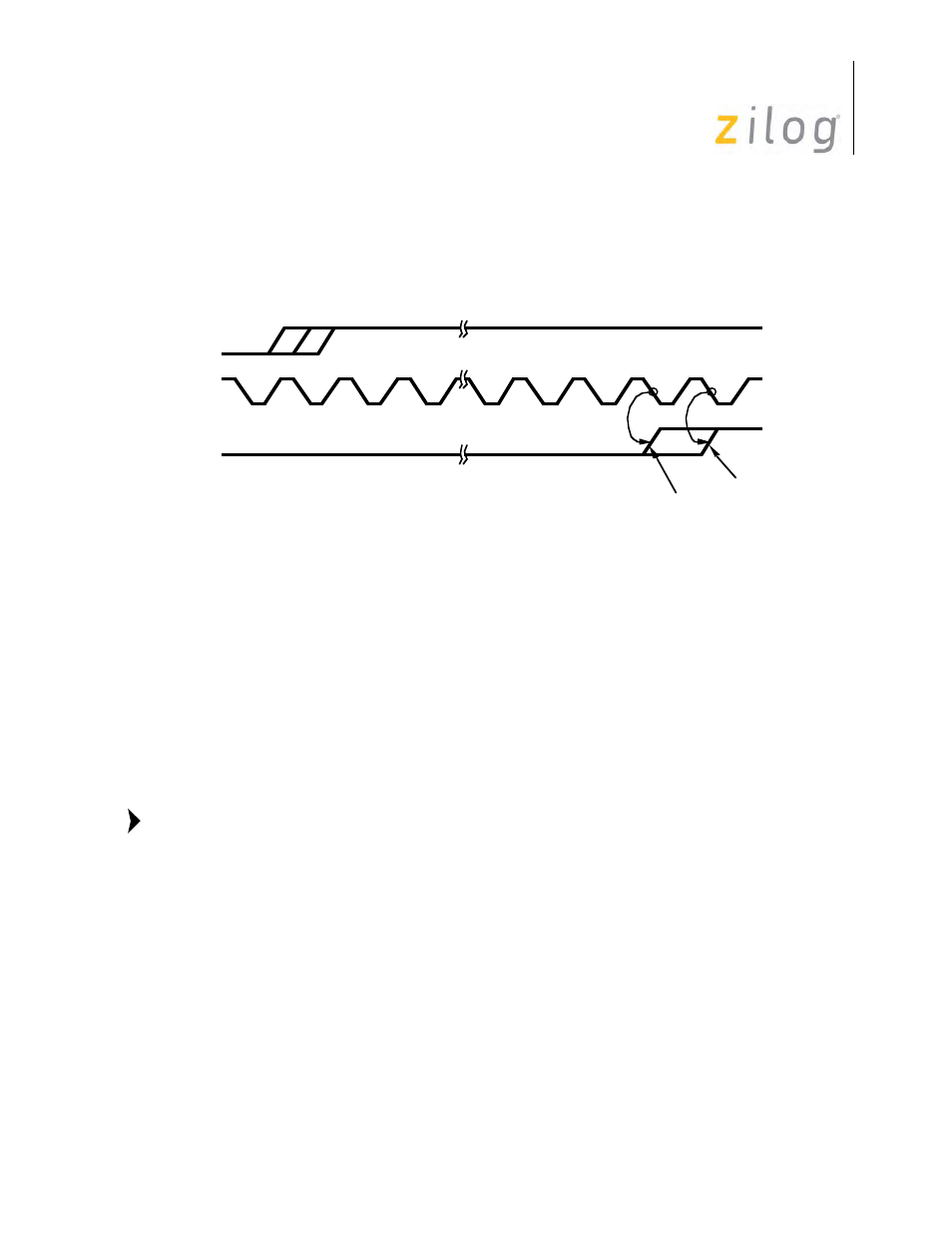

Wait On Receive Timing (ii)

DMA Requests

The two DMA request pins /W//REQ and /DTR//REQ can be programmed for DMA requests. The

/W//REQ pin is used as either a transmit or a receive request, and the /DTR//REQ pin can be used

as a transmit request only. For full-duplex operation, the /W//REQ is used for receive, and the /

DTR//REQ is used for transmit. These modes are described below.

DMA Request on ESCC

Transmit DMA request is also affected by WR7' bit D5. As noted earlier, WR7' D5 affects both the

transmit interrupt and DMA request generation similarly.

WR7' D3 is ignored by the Receive Request function. This allows a DMA to transfer all

bytes out of the Receive FIFO and still maintain the full advantage of the FIFO when the

DMA has a long latency response acquiring the data bus.

Bit D5 of WR7' is set to 1 after reset to maintain maximum compatibility with SCC designs. This

is necessary because if WR7' D5=0 when the request function is enabled, requests are made in

rapid succession to fill the FIFO. Consequently, some designs which require an edge to be

detected for each data transfer may not recover fast enough to detect the edges. This is handled by

programming WR7' D5=1, or changing the DMA to be level sensitive instead of edge sensitive.

Programming WR7' D5=0 has the advantage of the DMA requesting to keep the FIFO full. There-

fore, if the CPU is busy, a significantly longer latency can be tolerated without the transmitter

under-running.

/RTxC

/WAIT

SYNC Modes

PCLK

1

2

3

4

5•••8

9

10

11

12

13

ASYNC Modes

Note: