Service (ius), Figure, Scc/escc user manual – Zilog Z80230 User Manual

Page 46

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

39

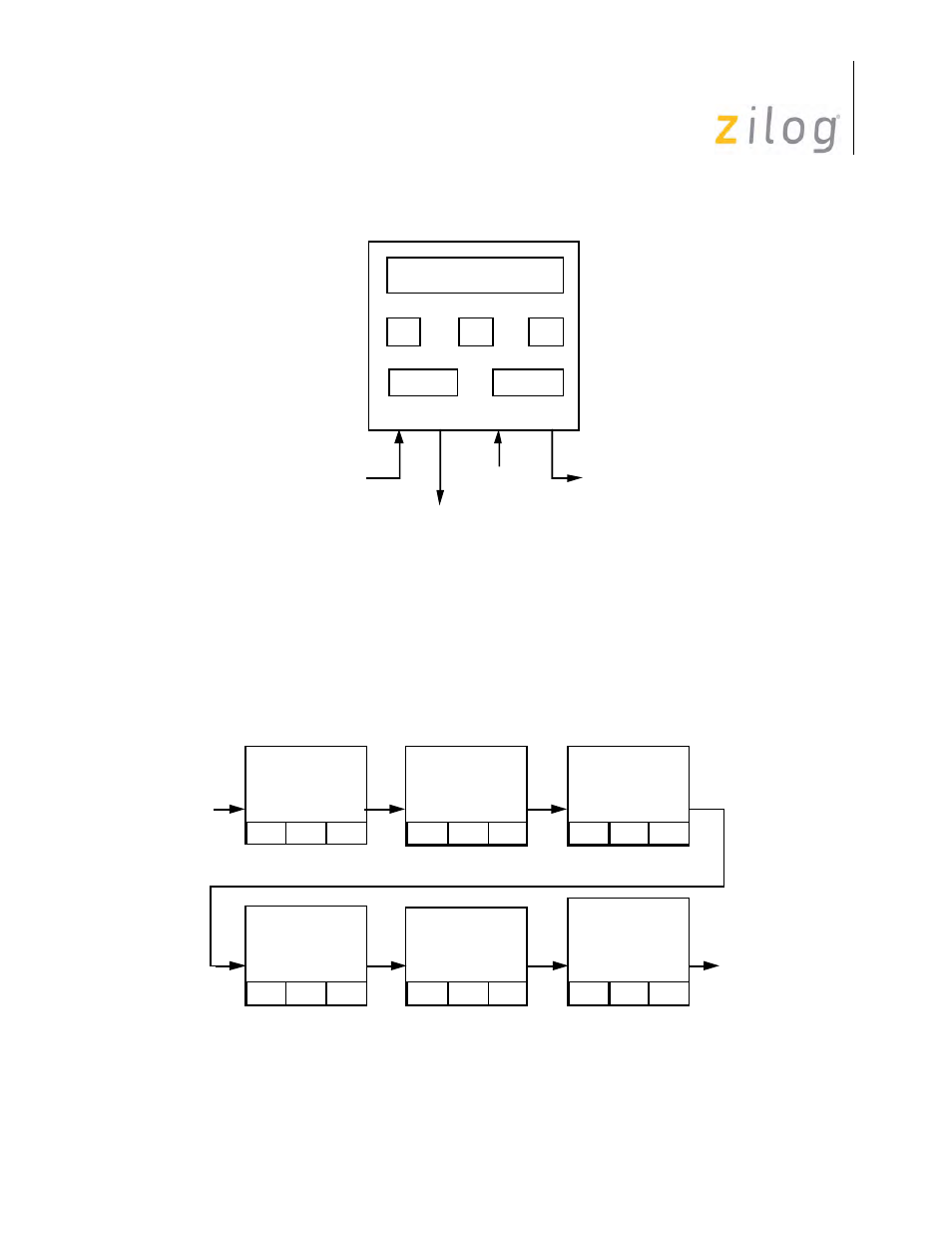

Peripheral Interrupt Structure

displays the internal priority resolution method to allow the highest priority interrupt to be

serviced first. Lower priority devices on the external daisy chain can be prevented from requesting

interrupts via the Disable Lower Chain bit in WR9 D2.

Internal Priority Resolution

IE

Interrupt Vector

From

CPU

Status

Decoder

MIE

DLC

IP

IUS

IEI

/INT

IEO

/INTACK

from Pullup

Resistor or IEO

line of Higher

Priority Device

To CPU

To IEI Input of

Lower Priority

Device

IE

Channel A

Receiver

(Highest Priority)

from

IEI

Pin

IUS

IP

IE

Channel A

Transmitter

IUS

IP

IEI

IEO

IEI

IEO

IE

Channel A

External/Status

Conditions

IUS

IP

IEI

IEO

IE

Channel B

Receiver

IUS

IP

IE

Channel B

Transmitter

IUS

IP

IEI

IEO

IEI

IEO

IE

Channel B

External/Status

Conditions

(Lowest

Priority)

IUS

IP

IEI

IEO

To

IEO

Pin