Read register 10 – Zilog Z80230 User Manual

Page 192

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

185

Read Register 10

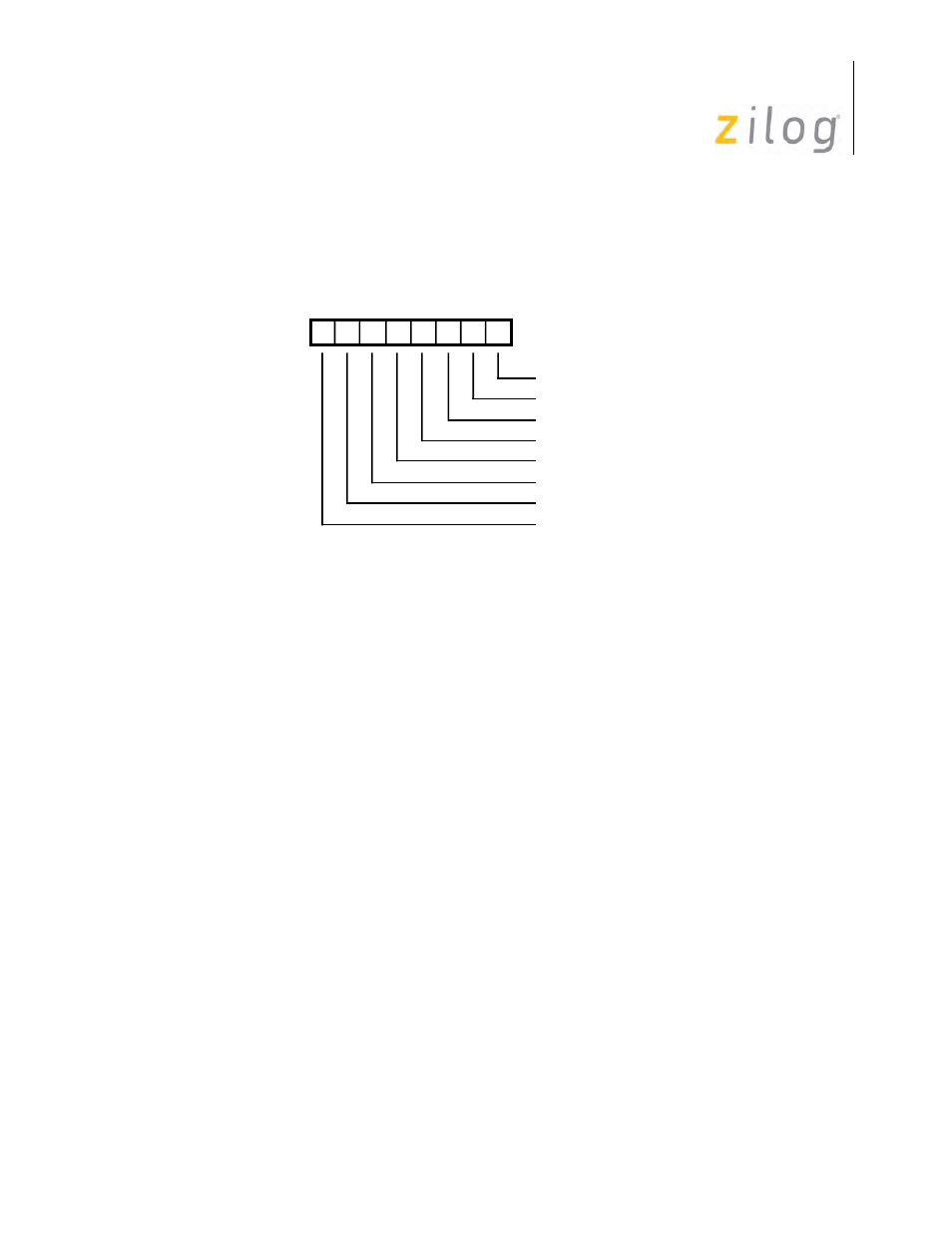

RR10 contains some miscellaneous status bits. Unused bits are always 0. Bit positions for RR10

are displayed in

Read Register 10

Bit 7: One Clock Missing status

While operating in the FM mode, the DPLL sets this bit to 1 when it does not see a clock edge on

the incoming lines in the window where it expects one. This bit is latched until reset by a Reset

Missing Clock or Enter Search Mode command in WR14. In the NRZI mode of operation and

while the DPLL is disabled, this bit is always 0.

Bit 6: Two Clocks Missing status

While operating in the FM mode, the DPLL sets this bit to 1 when it does not see a clock edge in

two successive tries. At the same time the DPLL enters the Search mode. This bit is latched until

reset by a Reset Missing Clock or Enter Search Mode command in WR14, bit 5-7. In the NRZI

mode of operation and while the DPLL is disabled, this bit is always 0.

Bit 4: Loop Sending status

This bit is set to 1 in SDLC Loop mode while the transmitter is in control of the Loop, that is,

while the SCC is actively transmitting on the loop. This bit is reset at all other times.

This bit can be polled in SDLC mode to determine when the closing flag has been sent.

Bit 1: On Loop status

This bit is set to 1 while the SCC is actually on loop in SDLC Loop mode. This bit is set to 1 in the

X21 mode (Loop mode selected while in monosync) when the transmitter goes active. This bit is 0

at all other times. This bit can also be pulled in SDLC mode to determine when the closing flag

has been sent.

D7 D6 D5 D4 D3 D2 D1 D0

Read Register 10

0

On Loop

0

0

Loop Sending

0

Two Clocks Missing

One Clock Missing