Scc/escc user manual – Zilog Z80230 User Manual

Page 72

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

65

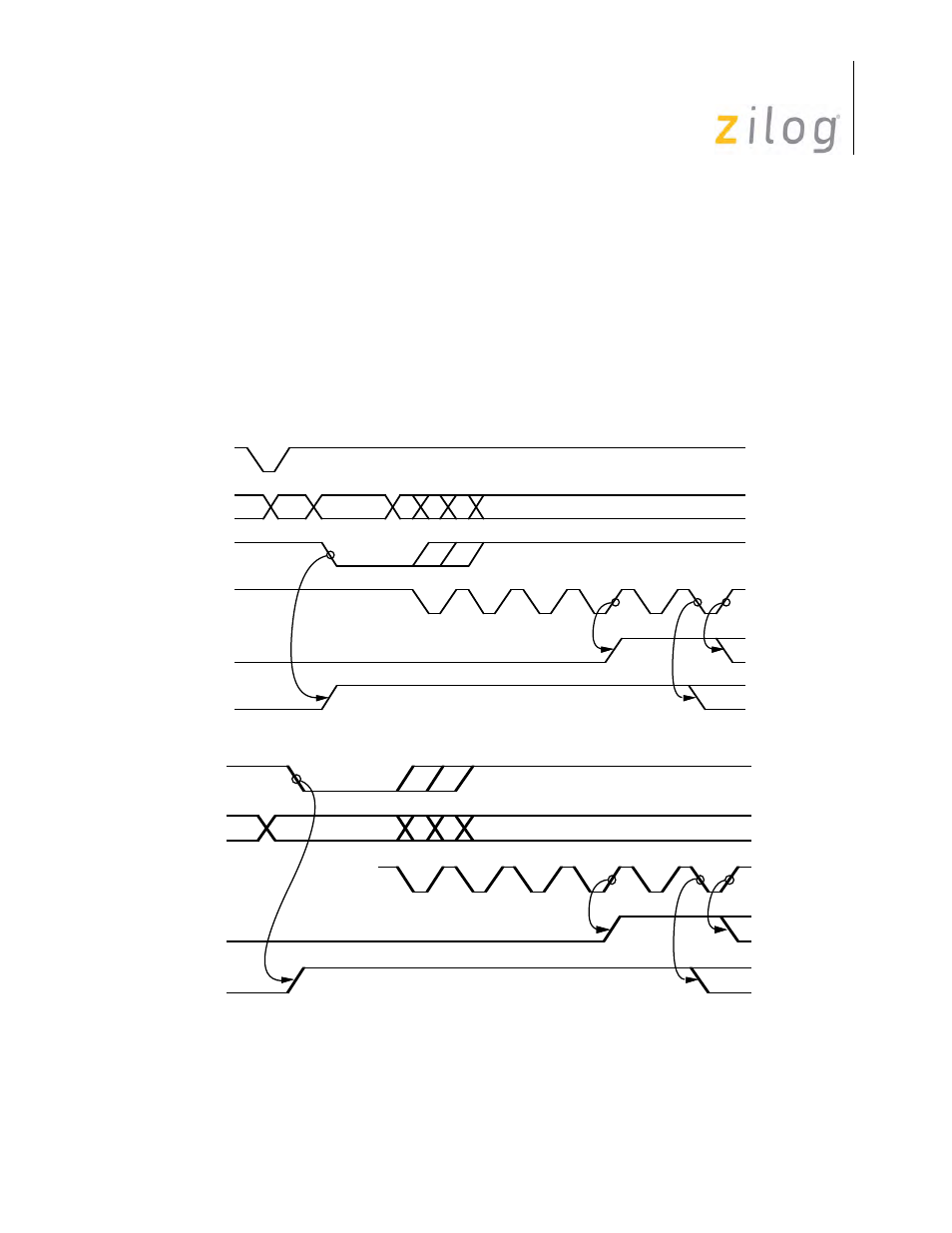

With only one exception, the /REQ pin directly follows the state of the transmit buffer (for the

ESCC as programmed by WR7' D5) in this mode. The SCC generates only one falling edge on /

REQ per character requested and the timing for this is displayed in

.

The one exception occurs in synchronous modes at the end of a CRC transmission. At the end of a

CRC transmission, when the closing flag or sync character is loaded into the Transmit Shift Regis-

ter, /REQ is pulsed High for one PCLK cycle. The DMA uses this falling edge on /REQ to write

the first character of the next frame to the SCC. In the case of the Z80X30, /REQ goes High in

response to the falling edge of DS, but only if the appropriate channel transmit buffer in the SCC is

accessed. This is displayed in

on page 61. In the case of the Z85X30, /REQ goes High in

response to the falling edge of /WR, but only when the appropriate channel transmit buffer in the

SCC is accessed. This is displayed in

Z80X30 Transmit Request Release

Z86X30 Transmit Request Release

/DS

/REQ

(/DTR//REQ)

PCLK

/REQ

(/W//REQ)

/AS

AD7-AD0

Transmit Data

WR8

/REQ

(/DTR//REQ)

PCLK

/REQ

(/W//REQ)

D7-D0

Transmit Data

/WR