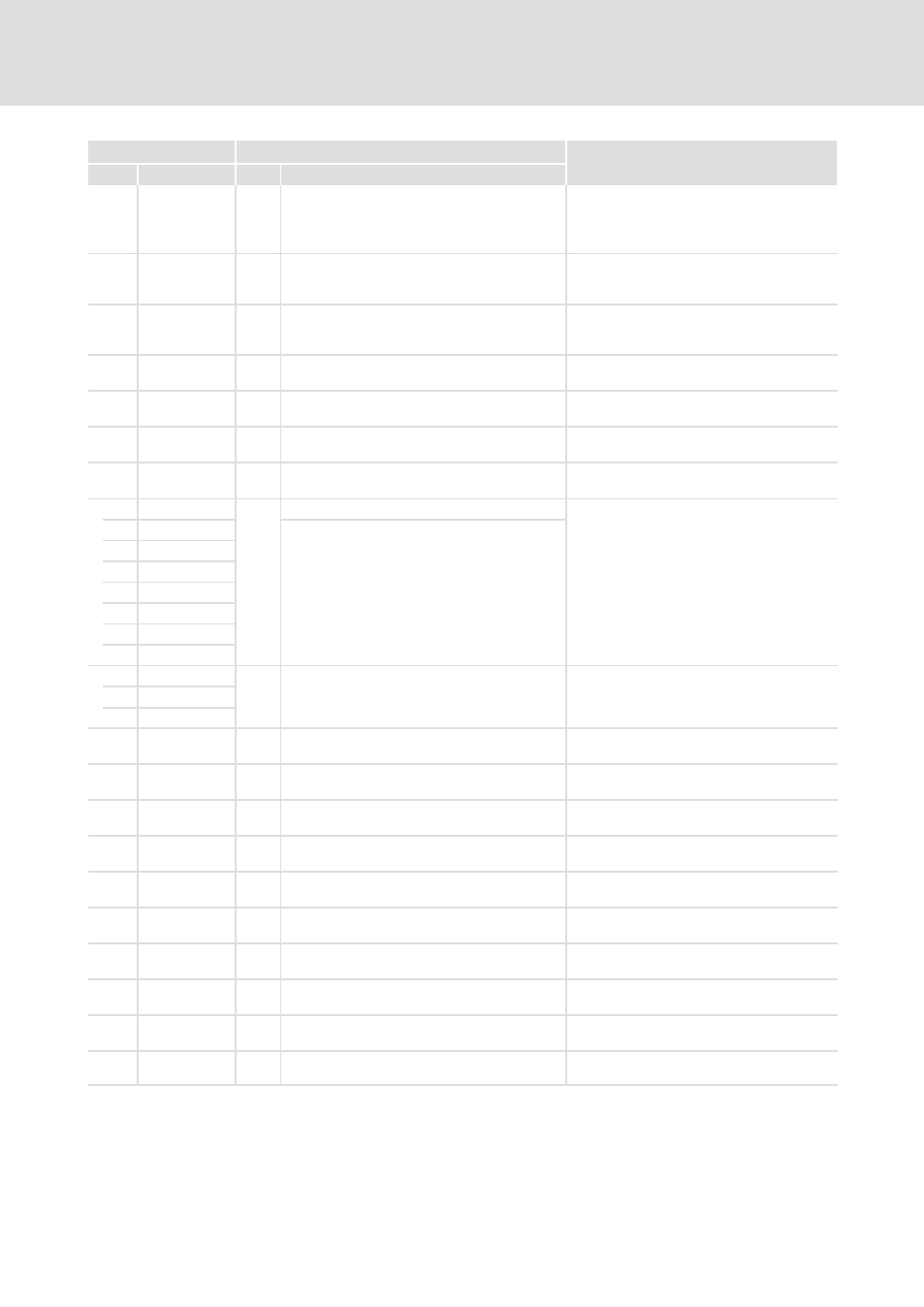

Configuration, Code table – Lenze EVS9332xK User Manual

Page 319

Configuration

Code table

8.4

l

8.4−45

EDSVS9332K EN 8.0−07/2013

IMPORTANT

Possible settings

Code

Selection

Lenze

Designation

No.

C0976

s

NACT

1000 FIXED0%

® Selection list 1 MFAIL

Configuration of input signal for comparison

value of threshold function

l

Starting point for U

2

controller

C0977

s

SET

1000 FIXED0%

® Selection list 1 MFAIL

Configuration of input signal for speed start

value

C0978

s

DC−SET

1000 FIXED0%

® Selection list 1 MFAIL

Configuration of input signal for DC−bus

voltage setpoint

C0980 MFAIL VP

0.500 0.001

{0.001}

31.000 MFAIL

Setting of the gain V

p

C0981 MFAIL TN

100

20

{1 ms}

2000 MFAIL

Setting of reset time T

n

C0982 MFAIL TIR

2.000 0.001

{0.001 s}

16.000 MFAIL

Setting of the acceleration time T

ir

C0983 RETRIGGER T

1.000 0.001

{0.001 s}

60.000 MFAIL

Retrigger time

C0988

g −199.99

{0.01 %}

199.99 MFAIL

Display of analog input signals

1 (C0970)

2 (C0973)

3 (C0974)

4 (C0975)

5 (C0976)

6 (C0977)

7 (C0978)

C0989

g

MFAIL

Display of digital input signals

1 (C0971)

2 (C0972)

C0990

s

IN

1000 FIXEDPHI−0

® Selection list 4 PHINT1

Configuration of input signal

C0991

s

RESET

1000 FIXED0

® Selection list 2 PHINT1

Configuration of reset signal

C0992 (C0990)

g −32767

{1}

32767 PHINT1

Display of input signal

C0993 (C0991)

g

PHINT1

Display of digital input signal

C0995 DIVISION

0

−31

{1}

31 PHDIV

Divisor in the power−of−two format (2

C0995

)

C0996

s

IN

1000 FIXED0INC

® Selection list 3 PHDIV

Configuration of input signal

C0997 (C0996)

g −2147483647

{1}

2147483647 PHDIV

Display of input signal

C1000 DIVISION

1

0

{1}

31 CONVPHA1

Divisor in the power−of−two format (2

C0995

)

C1001

s

IN

1000 FIXED0INC

® Selection list 3 Configuration of CONVPHA1 input

C1002 (C1001)

g −2147483647

{1}

2147483647 CONVPHA1

Display of input signal